**CONFIDENTIAL**

**CYNSE10512 CYNSE10256 CYNSE10128**

# Ayama™ 10000 **Network Search Engine**

**Cypress Semiconductor Corporation** Document #: 38-02069 Rev. \*F

3901 North First Street

٠

San Jose, CA 95134 408-943-2600 Revised July 13, 2004

[+] Feedback

# TABLE OF CONTENTS

| 1.0 FEATURES                                                                   | 10 |

|--------------------------------------------------------------------------------|----|

| 2.0 OVERVIEW                                                                   | 11 |

| 3.0 DEVICE ARCHITECTURE OVERVIEW                                               | 13 |

| 3.1 Data Array, Mask Array and Table Widths                                    | 13 |

| 3.2 Data and Mask Addressing                                                   |    |

| 3.3 Successful Search and Multiple Match Arbitration                           |    |

| 4.0 SIGNALS DESCRIPTION                                                        |    |

| 5.0 FUNCTIONAL DESCRIPTION                                                     |    |

|                                                                                |    |

| 5.1 Modes of Operation                                                         |    |

| 5.1.1 Non-Enhanced Mode                                                        |    |

| 5.1.2 Enhanced Mode                                                            |    |

| 5.1.2.1 Mini-Rey                                                               |    |

| 5.1.2.3 Parity                                                                 |    |

| 5.1.2.4 MultiSearch                                                            |    |

| 5.1.2.5 Enhanced Learn Operation                                               |    |

| 5.2 I/O Interfaces                                                             | 23 |

| 5.2.1 ASIC Interface                                                           | 24 |

| 5.2.2 SRAM Interface                                                           |    |

| 5.2.3 Cascade Interface                                                        |    |

| 5.3 Output Signals Default Driver/Last Device Designation (LRAM and LDEV)      |    |

| 5.4 Registers                                                                  |    |

| 5.4.1 Comparand Register (CMPR)                                                |    |

| 5.4.2 Global Mask Register (GMR)                                               |    |

| 5.4.3 Search Successful Register (SSR)                                         |    |

| 5.4.4 Command Register (COMMAND)                                               |    |

| 5.4.5 Information Register (INFO)                                              |    |

| 5.4.6 Read Burst Address Register (RBURREG)                                    |    |

| 5.4.7 Write Burst Address Register (WBURREG)                                   |    |

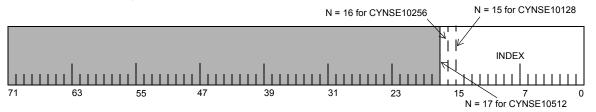

| 5.4.8 Next-free Address Register (NFA)                                         |    |

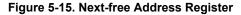

| 5.4.9 Configuration Register (CONFIG)                                          |    |

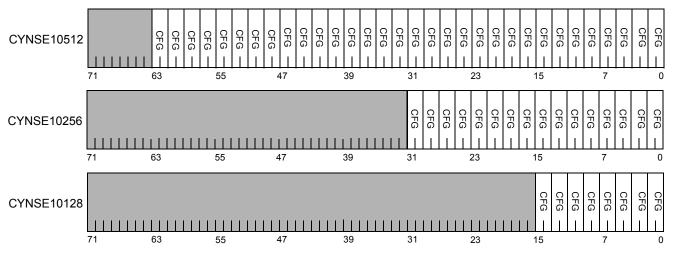

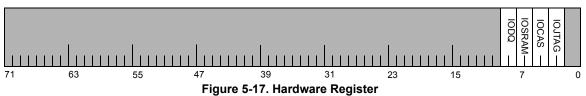

| 5.4.10 Hardware Register (HARDWARE)                                            |    |

| 5.4.11 Parity Control Register (PARITY)<br>5.4.12 Control Register (CPR[0:15]) |    |

| 5.4.13 Search Result Register (SRR[15:0])                                      |    |

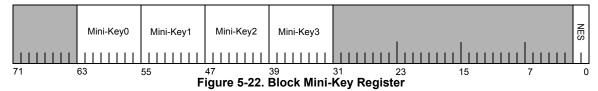

| 5.4.14 Block Mini-Key Register (BMR)                                           |    |

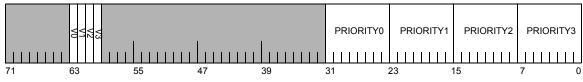

| 5.4.15 Block Priority Register (BPR)                                           |    |

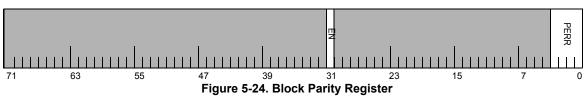

| 5.4.16 Block Parity Register (BPAR)                                            |    |

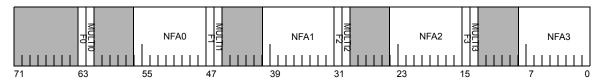

| 5.4.17 Block NFA Register (BNFA)                                               |    |

| 5.4.18 Block Priority Register Aliases (BPRA)                                  |    |

| 5.5 Multi-Hit Description                                                      |    |

| 5.6 Clocks                                                                     |    |

| 5.7 Phase-Locked Loop                                                          |    |

| 5.8 Pipeline Latency                                                           |    |

| 5.9 DQ Bus Encoding of Ayama 10000 Address Space                               |    |

| 5.9 Do bus Encounty of Ayama Tooloo Address Space                              |    |

| 5.9.2 Addressing the Internal Registers                                        |    |

|                                                                                |    |

# CONFIDENTIAL PRELIMINARY

# TABLE OF CONTENTS (continued)

| 5.10 Depth Cascading                                                                                    | 45  |

|---------------------------------------------------------------------------------------------------------|-----|

| 5.10.1 Depth Cascading up to Eight Devices in One Block                                                 | 45  |

| 5.10.2 Depth Cascading up to 31 Devices in 4 Blocks                                                     |     |

| 5.10.3 Depth Cascading for a FULL Signal                                                                |     |

| 5.11 Device Selection in a Cascaded System                                                              |     |

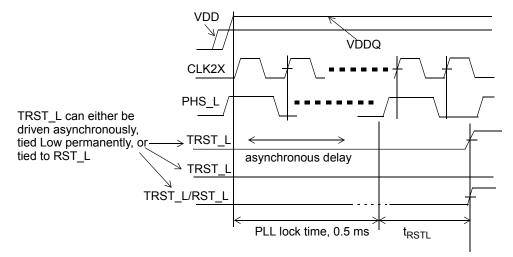

| 5.12 Power-up Sequence                                                                                  | 49  |

| 6.0 OPERATIONS AND TIMING DIAGRAMS                                                                      | 50  |

| 6.1 Command Encoding                                                                                    | 50  |

| 6.2 Command Bus Parameters                                                                              | 50  |

| 6.2.1 Non-Enhanced Mode (EMODE = 0)                                                                     |     |

| 6.2.2 Enhanced Mode (EMODE = 1) with MultiSearch Disabled (MSE = 0)                                     | 51  |

| 6.2.3 Enhanced Mode (EMODE = 1) with MultiSearch Enabled (MSE = 1)                                      |     |

| 6.3 Read Command                                                                                        |     |

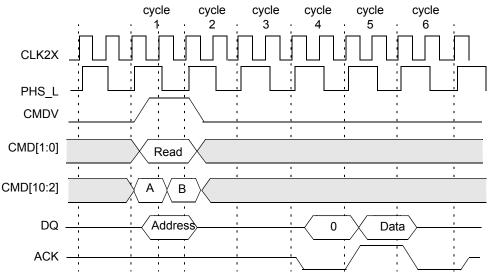

| 6.3.1 Single Read                                                                                       |     |

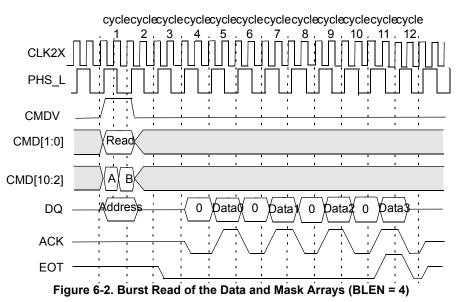

| 6.3.2 Burst Read                                                                                        |     |

| 6.3.3 Read Parity                                                                                       |     |

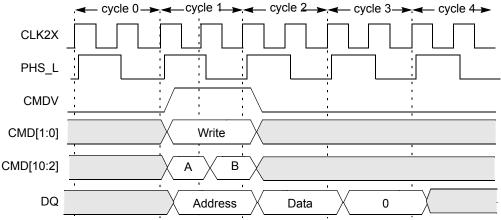

| 6.4 Write Command                                                                                       |     |

| 6.4.1 Single Write                                                                                      |     |

| 6.4.2 Burst Write                                                                                       |     |

| 6.5 Search Command                                                                                      |     |

| 6.5.1 Mixed-size Single Searches with One Device on Tables Configured with Different Widths             |     |

| 6.5.2 Mixed-size Multi Searches with One Device on Tables Configured with Different Widths              |     |

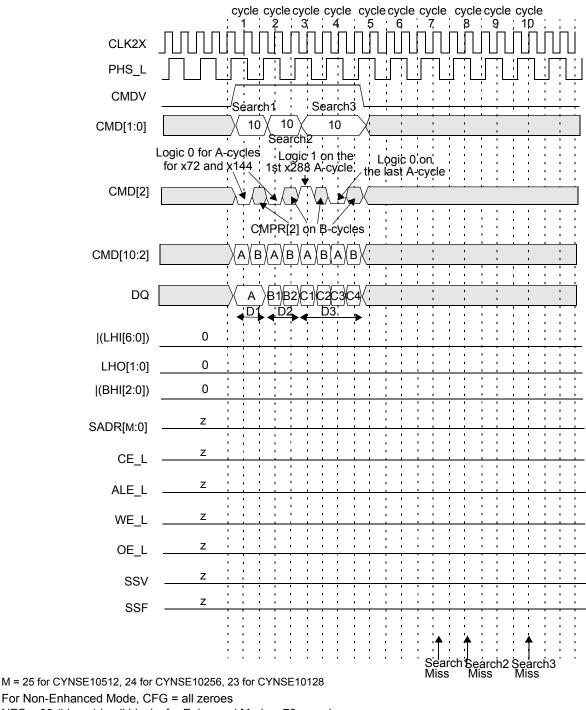

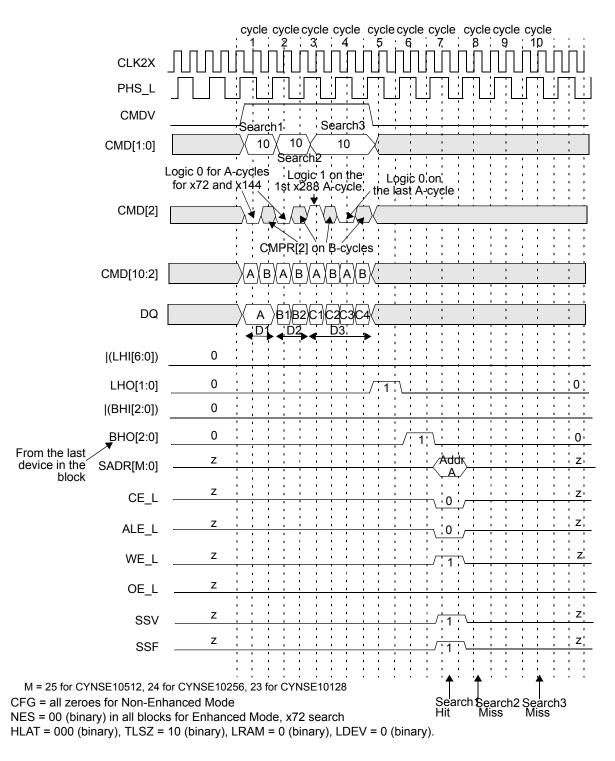

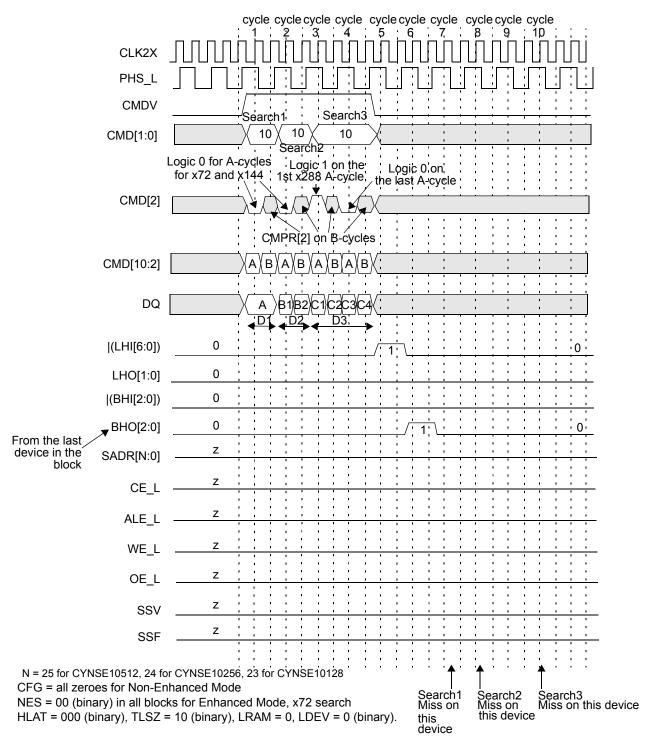

| 6.5.3 72-bit Single Search for 1 device or cascade up to eight devices                                  |     |

| 6.5.4 72-bit MultiSearch for One Device or Cascade Up to Eight Devices                                  |     |

| 6.5.5 144-bit Single Search for Cascade Up to 31 Devices                                                |     |

| 6.5.6 576-bit Single Search for One Device or Cascade up to Eight Devices                               |     |

| 6.5.7 576-bit MultiSearch for One Device or Cascade up to Eight Devices                                 | 89  |

| 6.5.8 Mixed-size Single Searches with 31 Devices on Tables Configured with Different Widths             |     |

| 6.5.9 Mixed-size Multi Searches with 8 Devices on Tables Configured with Different Widths               |     |

| 6.6 Learn Command                                                                                       |     |

| 6.6.1 Non-Enhanced Mode                                                                                 |     |

| 6.6.2 Enhanced Mode                                                                                     |     |

| 6.6.3 Learn Operation on Depth-Cascaded Table                                                           |     |

| 6.7 SRAM PIO Access                                                                                     |     |

| 6.7.1 SRAM Read with a Table of One Device                                                              |     |

| 6.7.2 SRAM Read with a Table of up to Eight Devices<br>6.7.3 SRAM Read with a Table of up to 31 Devices |     |

| 6.7.4 SRAM Write with a Table of One Device                                                             |     |

| 6.7.5 SRAM Write with a Table of up to Eight Devices                                                    |     |

| 6.7.6 SRAM Write with Table(s) Consisting of up to 31 Devices                                           |     |

| 6.8 Timing Sequences for Back-to-Back Operations                                                        |     |

| 6.9 Full Signal Timing Diagram                                                                          |     |

|                                                                                                         |     |

| 7.0 JTAG (IEEE 1149.1)                                                                                  |     |

| 8.0 POWER CONSUMPTION                                                                                   |     |

| 9.0 ELECTRICAL SPECIFICATIONS                                                                           | 137 |

CONFIDENTIAL PRELIMINARY

# TABLE OF CONTENTS (continued)

| 10.0 AC TIMING PARAMETERS, WAVEFORMS AND TEST CONDITIONS | 138 |

|----------------------------------------------------------|-----|

| 10.1 AC Timing Parameters and Waveforms with CLK2X       |     |

| 10.2 AC Timing Parameters and Waveforms with CLK1X       | 140 |

| 10.3 AC Test Conditions and Output Loads                 | 143 |

| 10.3.1 LVCMOS 2.5V/1.8V                                  |     |

| 10.3.2 HSTL I/II                                         | 144 |

| 11.0 PIN ASSIGNMENT AND PINOUT DIAGRAM                   | 145 |

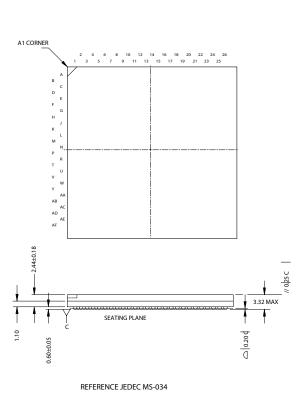

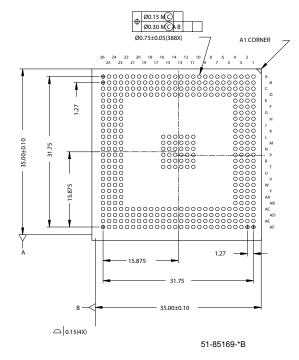

| 12.0 PACKAGE DIAGRAMS                                    | 151 |

| 13.0 ORDERING INFORMATION                                | 151 |

# LIST OF FIGURES

| Figure 2-1. Ayama™ 10000 Block Diagram                                        | 11 |

|-------------------------------------------------------------------------------|----|

| Figure 2-2. Example of Switch/Router Implementation Using Ayama 10000         |    |

| Figure 3-1. Ayama 10000 Database Table Widths                                 |    |

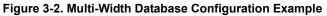

| Figure 3-2. Multi-Width Database Configuration Example                        |    |

| Figure 3-3. Addressing the Ayama 10000 Data and Mask Arrays                   |    |

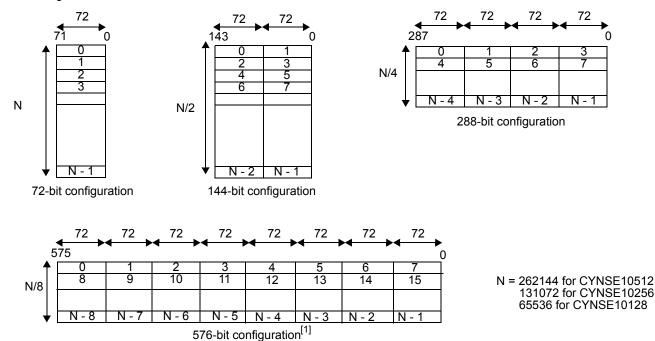

| Figure 5-1. Blocks and Block Registers Association                            | 19 |

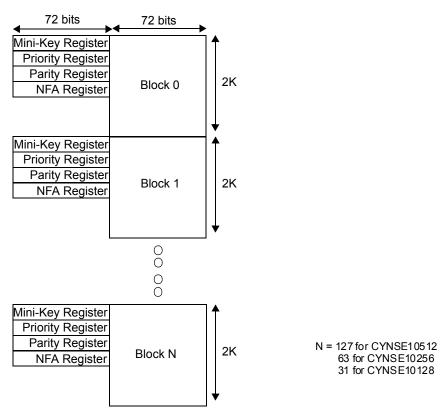

| Figure 5-2. Mini-Key Register Contents                                        |    |

| Figure 5-3. Sub-Blocks and Soft Priority Associations                         |    |

| Figure 5-4. Timing Diagram of a DQ Bus Parity Error (288-bit Search, TLSZ=00) |    |

| Figure 5-5. Timing Diagram of a Core Parity Error (TLSZ=00)                   |    |

| Figure 5-6. MultiSearch Operation Overview                                    |    |

| Figure 5-7. Ayama 10000 I/O Interfaces                                        |    |

| Figure 5-8. Comparand Register Selection During Search and Learn Instructions |    |

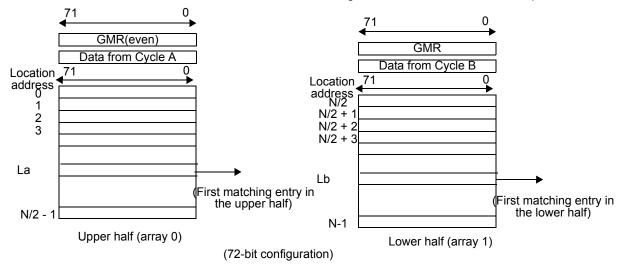

| Figure 5-9. Addressing the Global Mask Register Array                         |    |

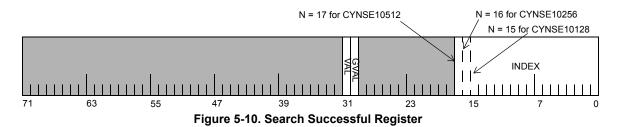

| Figure 5-10. Search Successful Register                                       |    |

| Figure 5-11. Command Register                                                 |    |

| Figure 5-12. Information Register                                             |    |

| Figure 5-13. Read Burst Register                                              |    |

| Figure 5-14. Write Burst Address Register                                     |    |

| Figure 5-15. Next-free Address Register                                       |    |

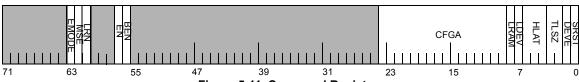

| Figure 5-16. Configuration Register                                           |    |

| Figure 5-17. Hardware Register                                                |    |

| Figure 5-18. Parity Control Register                                          |    |

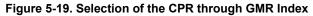

| Figure 5-19. Selection of the CPR through GMR Index                           |    |

| Figure 5-20. Control Register                                                 |    |

| Figure 5-21. Search Result Register                                           |    |

| Figure 5-22. Block Mini-Key Register                                          |    |

| Figure 5-23. Block Priority Register                                          |    |

| Figure 5-24. Block Parity Register                                            |    |

| Figure 5-25. Block NFA Register                                               |    |

| Figure 5-26. Block Priority Register Aliases                                  |    |

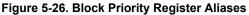

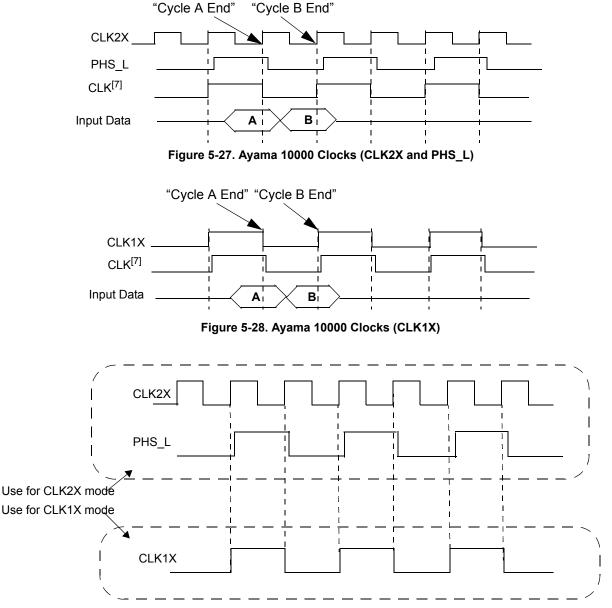

| Figure 5-27. Ayama 10000 Clocks (CLK2X and PHS_L)                             |    |

| Figure 5-28. Ayama 10000 Clocks (CLK1X)                                       |    |

| Figure 5-29. Ayama 10000 Clocks for All Timing Diagrams                       |    |

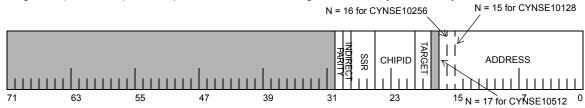

| Figure 5-30. Data Array, Mask Array and External SRAM Address Space Encoding  |    |

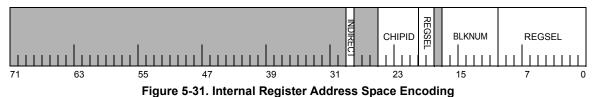

| Figure 5-31. Internal Register Address Space Encoding                         |    |

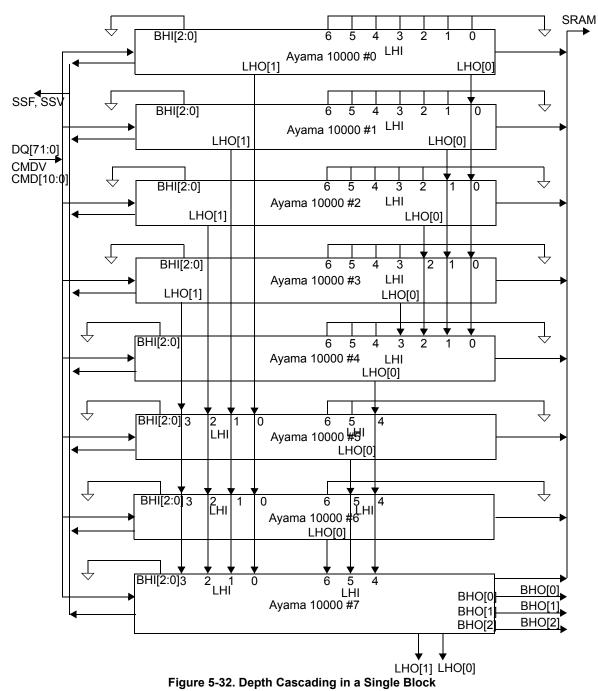

| Figure 5-32. Depth Cascading in a Single Block                                |    |

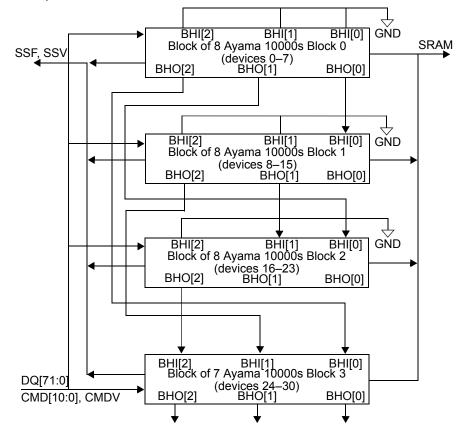

| Figure 5-33. Depth Cascading 4 Blocks                                         |    |

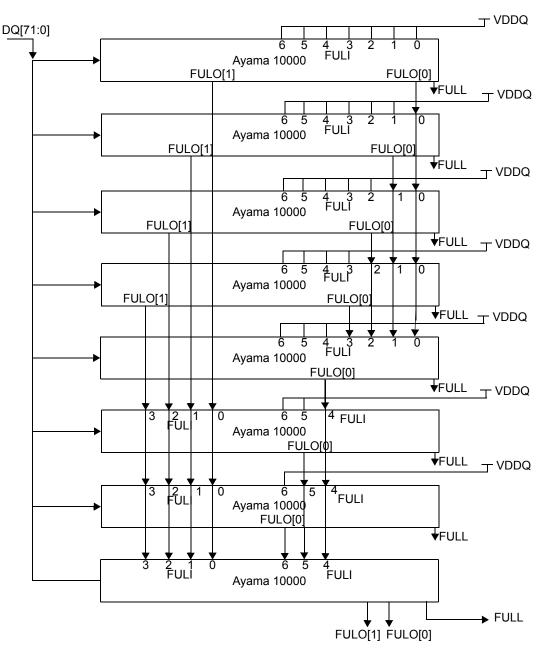

| Figure 5-34. FULL Signal Generation in a Cascaded Table                       |    |

| Figure 5-35. Proper Power-up Sequence                                         |    |

| Figure 6-1. Single-Location Read Cycle Timing                                 | 52 |

| Figure 6-2. Burst Read of the Data and Mask Arrays (BLEN = 4)                 |    |

| Figure 6-3. Single Write Cycle Timing                                         |    |

| Figure 6-4. Burst Write of the Data and Mask Arrays (BLEN = 4)                | 55 |

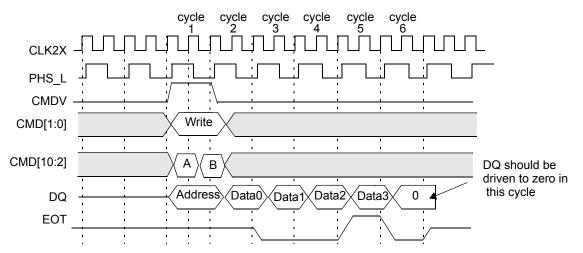

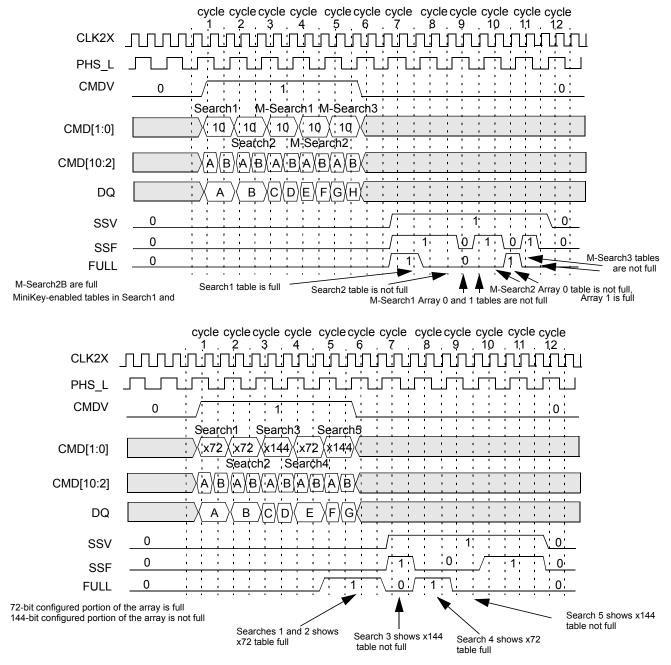

| Figure 6-5. Timing Diagram for Mixed Single Search (One Device)               | 57 |

| Figure 6-6. Multiwidth Configurations Using CYNSE10512 as an Example          | 58 |

| Figure 6-7. Timing Diagram for Mixed MultiSearch (One Device)                 |    |

| Figure 6-8. Multiwidth Configurations Using CYNSE10512 as an Example          |    |

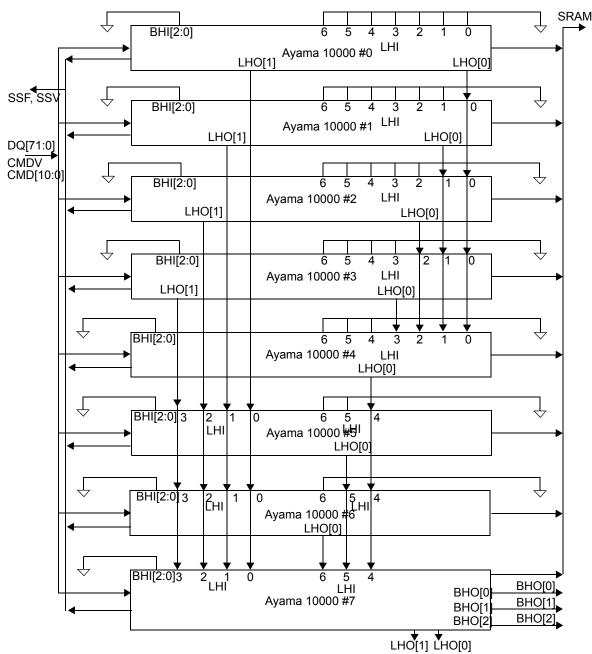

| Figure 6-9. Hardware Diagram for a Table with Eight Devices                   |    |

# LIST OF FIGURES (continued)

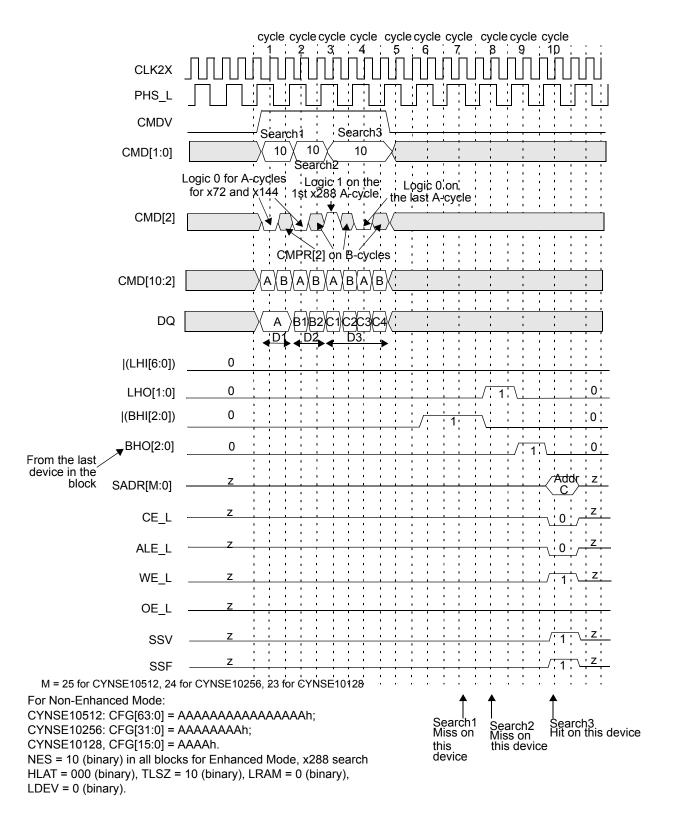

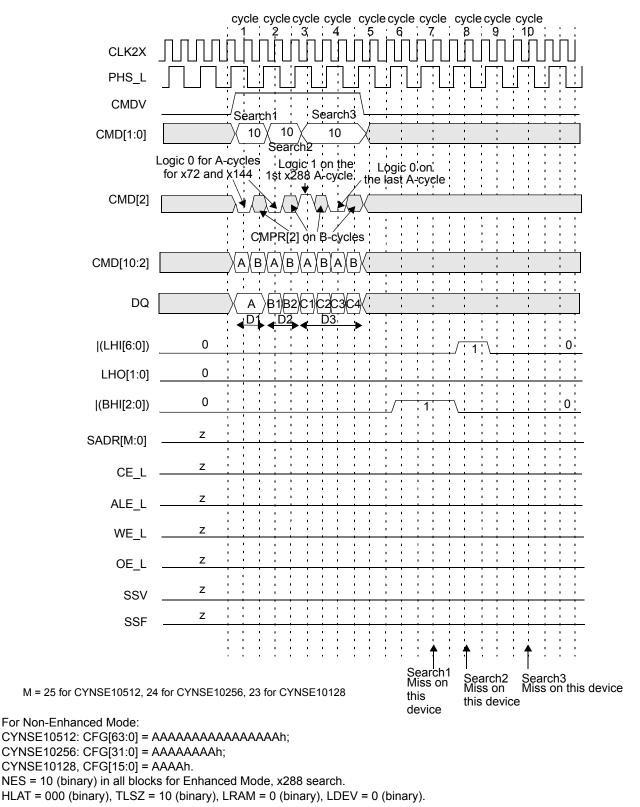

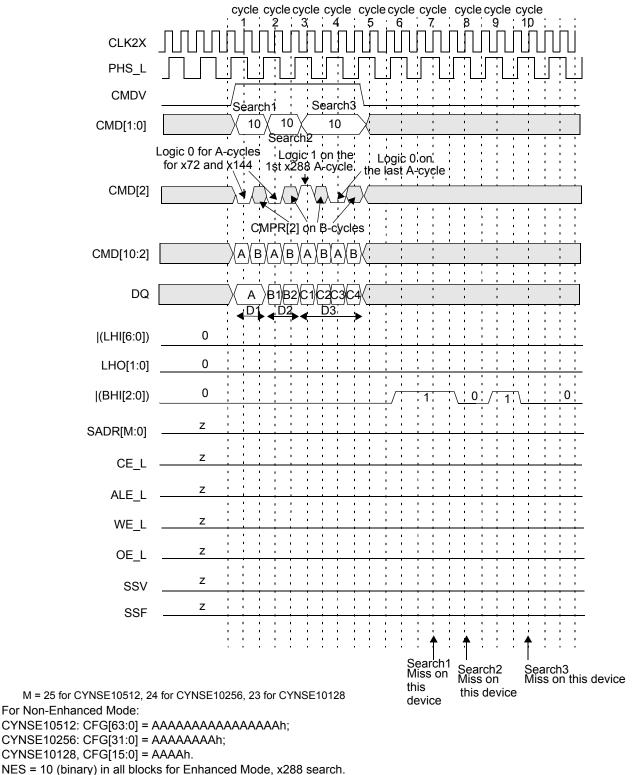

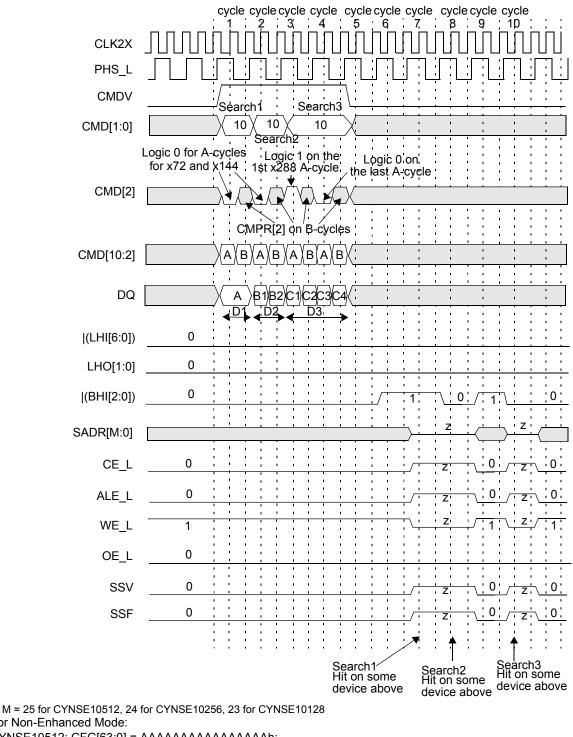

| Figure 6-10  | Timing Diagram for 72-bit Search Device Number 0                            | 62    |

|--------------|-----------------------------------------------------------------------------|-------|

|              | Timing Diagram for 72-bit Search Device Number 1                            |       |

|              | Timing Diagram for 72-bit Search Device Number 7 (Last Device)              |       |

|              | ×72 Table with Eight Devices                                                |       |

|              | Hardware Diagram for a Table with Eight Devices for MultiSearch             |       |

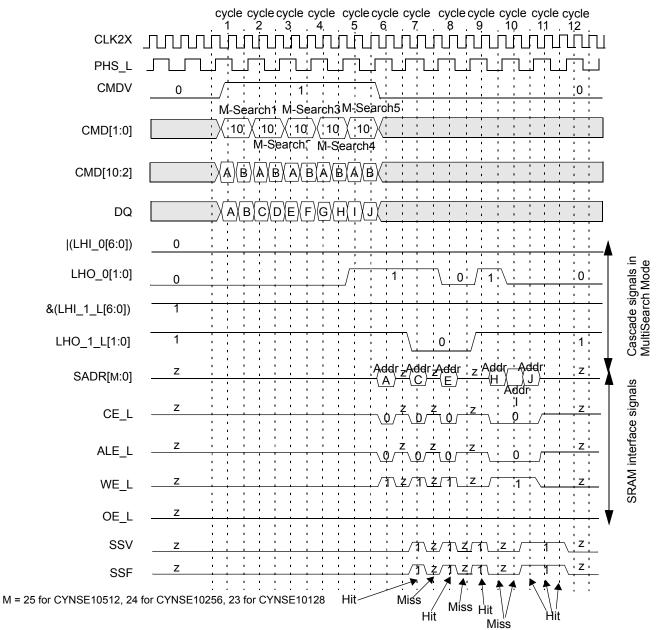

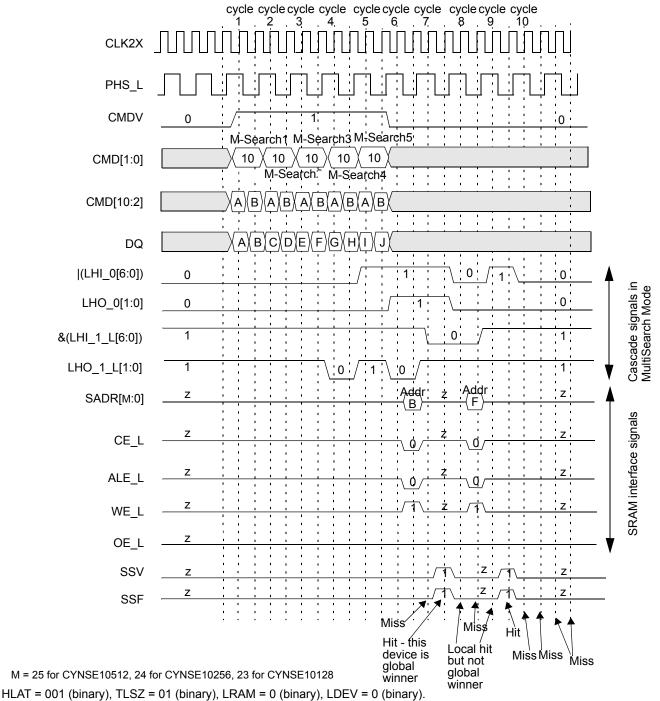

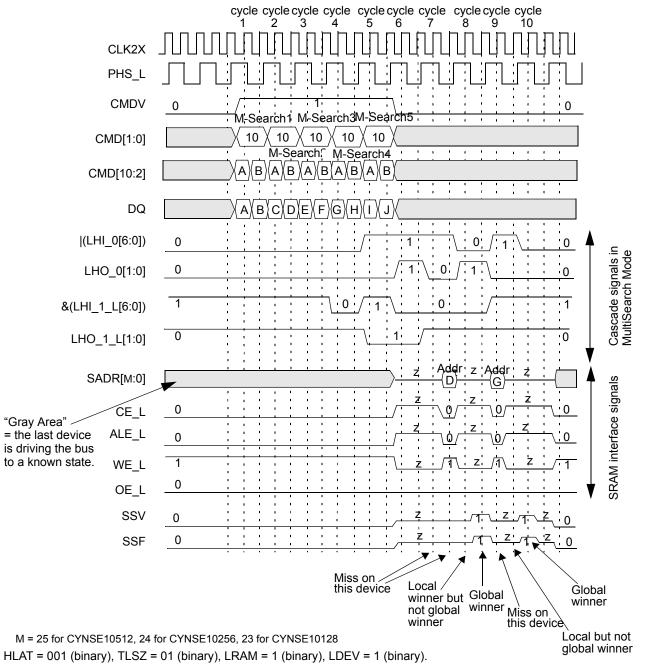

|              | Timing Diagram for 72-bit MultiSearch Device Number 0                       |       |

|              | Timing Diagram for 72-bit MultiSearch Device Number 1                       |       |

| Figure 6-17. | Timing Diagram for 72-bit MultiSearch Device Number 7 (Last Device)         | 70    |

| Figure 6-18. | ×72 Table with in MultiSearchMode                                           | 71    |

| Figure 6-19. | Hardware Diagram for a Table with 31 Devices                                | 73    |

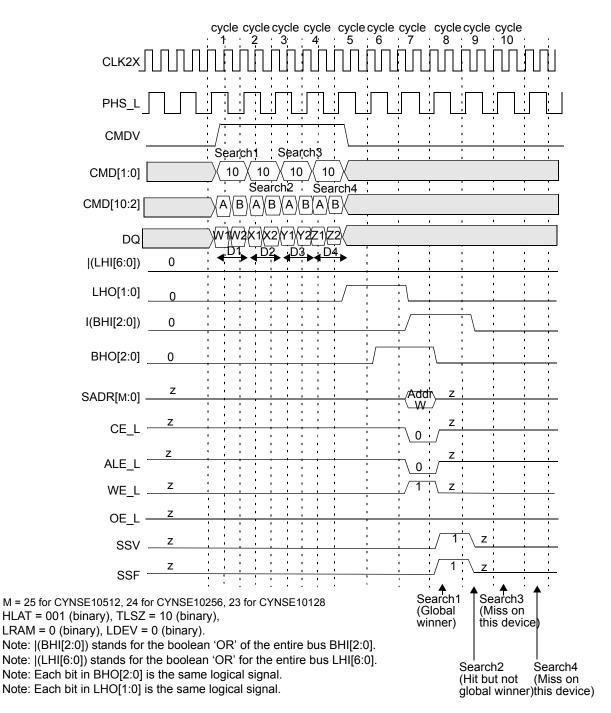

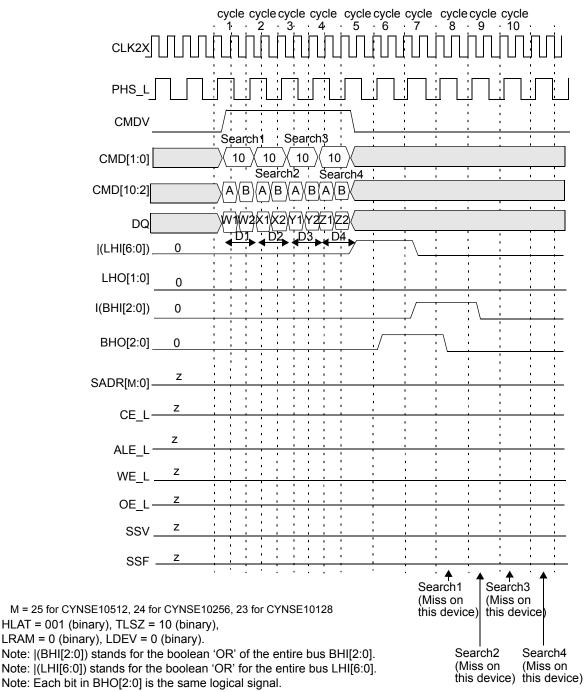

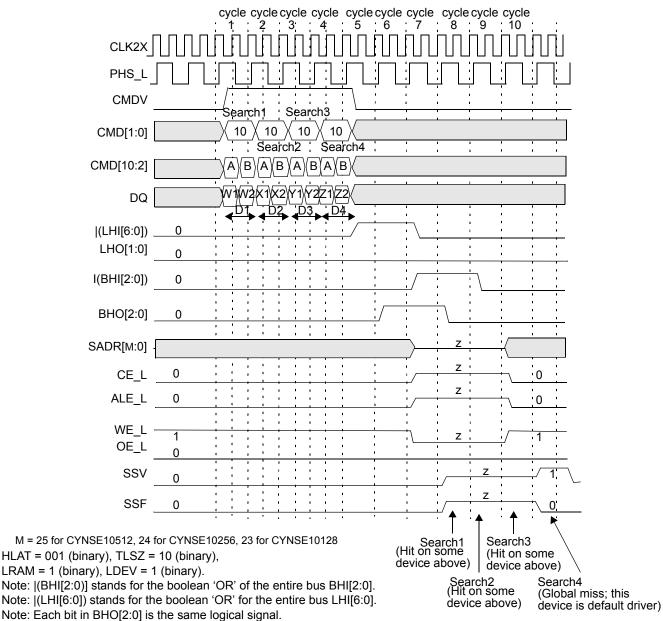

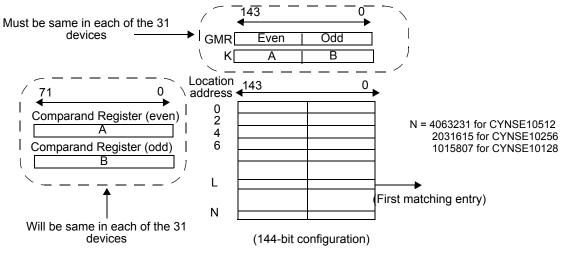

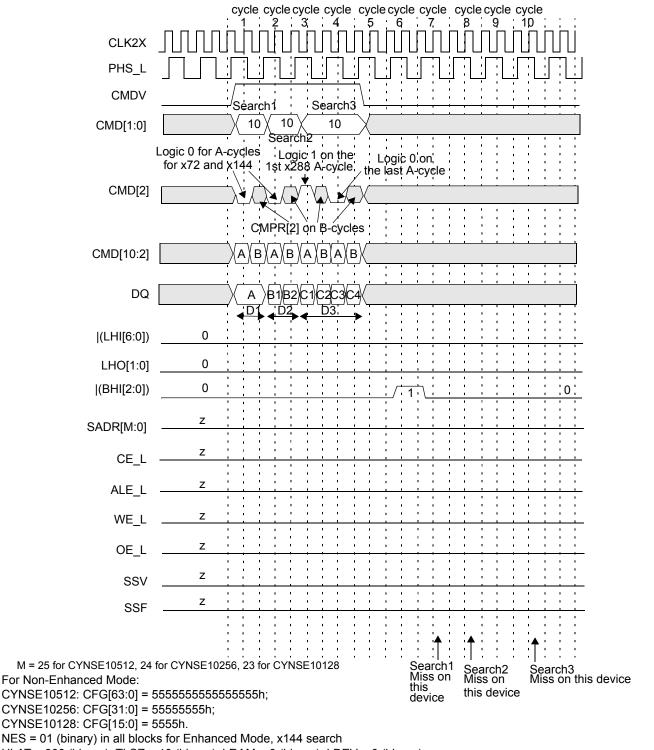

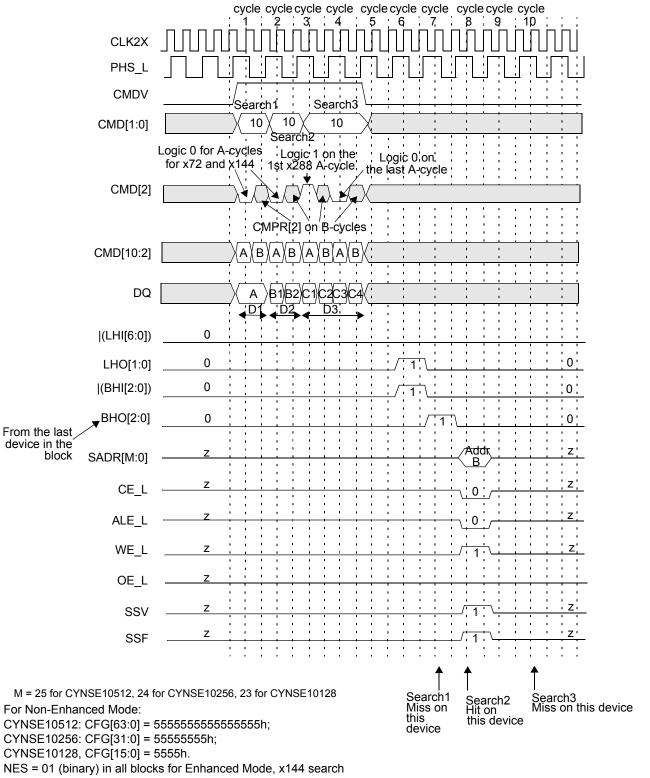

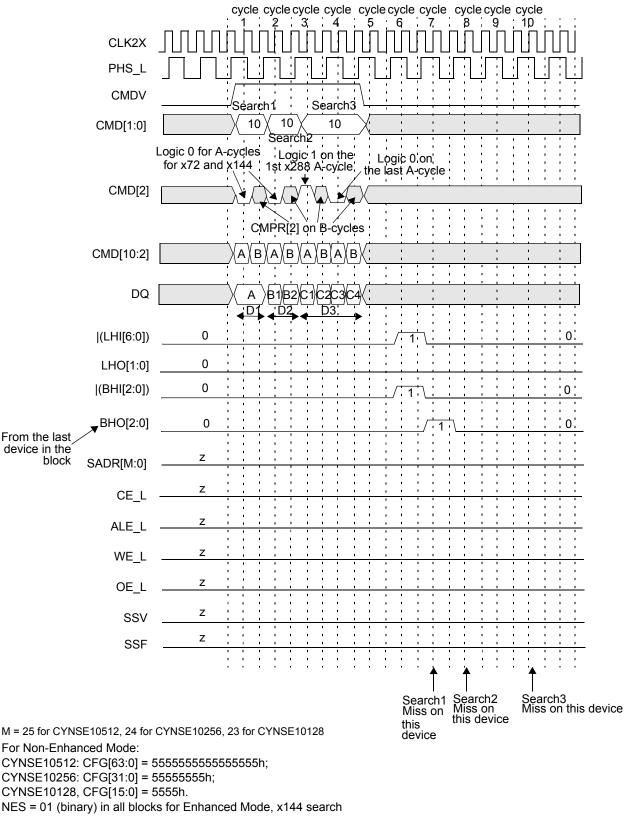

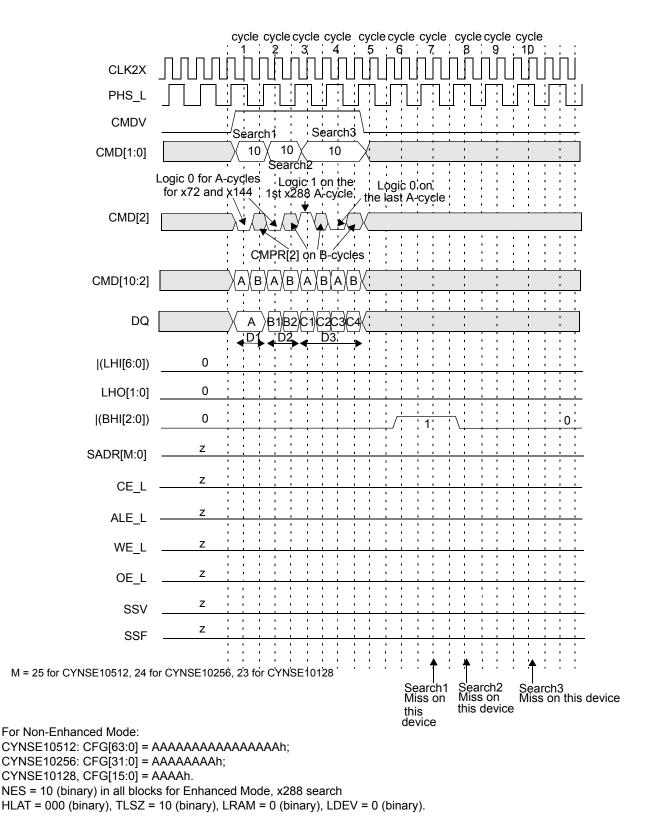

|              | 144-bit Search for Devices in Block #0 and Above Block #1 Winning Device    |       |

| •            | 144-bit Search Timing Diagram for Block #1 Global Winning Device            |       |

| •            | 144-bit Search Timing Diagram for Devices Below Block #1 Winning Device     |       |

| •            | 144-bit Search Timing Diagram for Devices Above Block #2 Winning Device     |       |

| •            | 144-bit Search Timing Diagram for Block #2 Global Winning Device            |       |

|              | 144-bit Search Timing Diagram for Devices Below Block #2 Winning Device     |       |

| •            | 144-bit Search Timing Diagram for Devices Above Block #3 Winning Device     |       |

| •            | 144-bit Search Timing Diagram for Block #3 Global Winning Device            |       |

| •            | 144-bit Search Diagram Below Block #3 Winning Device Except the Last Device |       |

|              | 144-bit Search Timing Diagram for Device Number 6 in Block #3               |       |

|              | ×144 Table with 31 Devices                                                  |       |

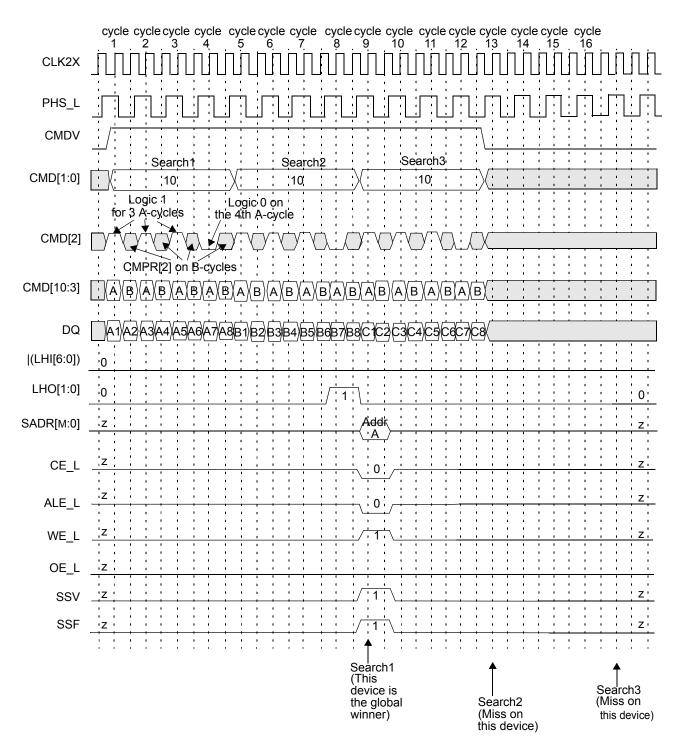

|              | Timing Diagram for 576-bit Single Search Device Number 0                    |       |

|              | Timing Diagram for 576-bit Single Search Device Number 1                    |       |

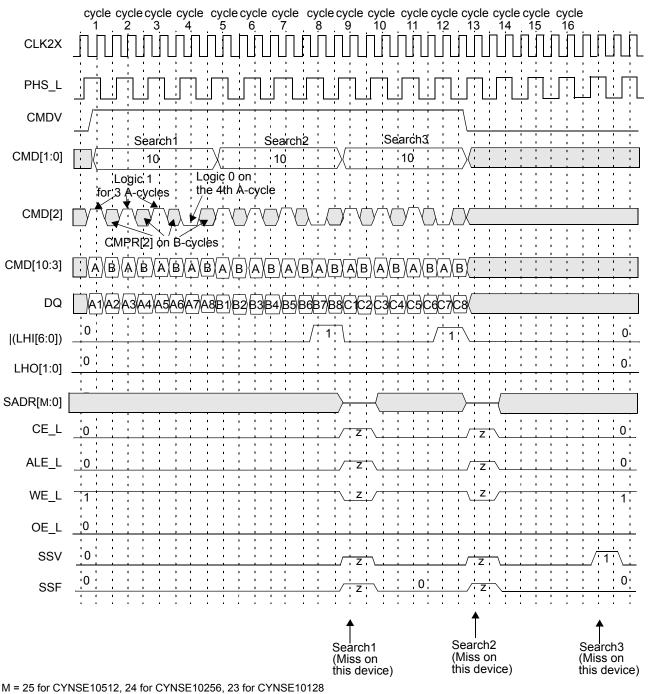

| •            | Timing Diagram for 576-bit Single Search Device Number 7 (Last Device)      |       |

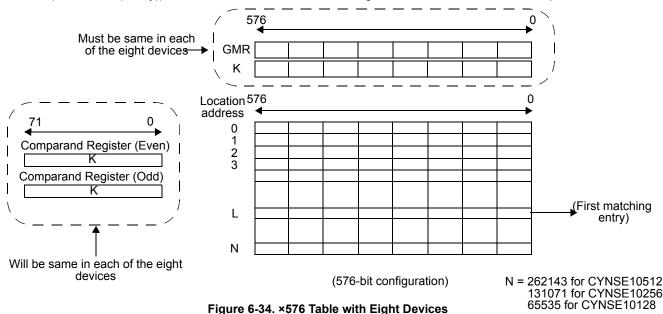

|              | ×576 Table with Eight Devices                                               |       |

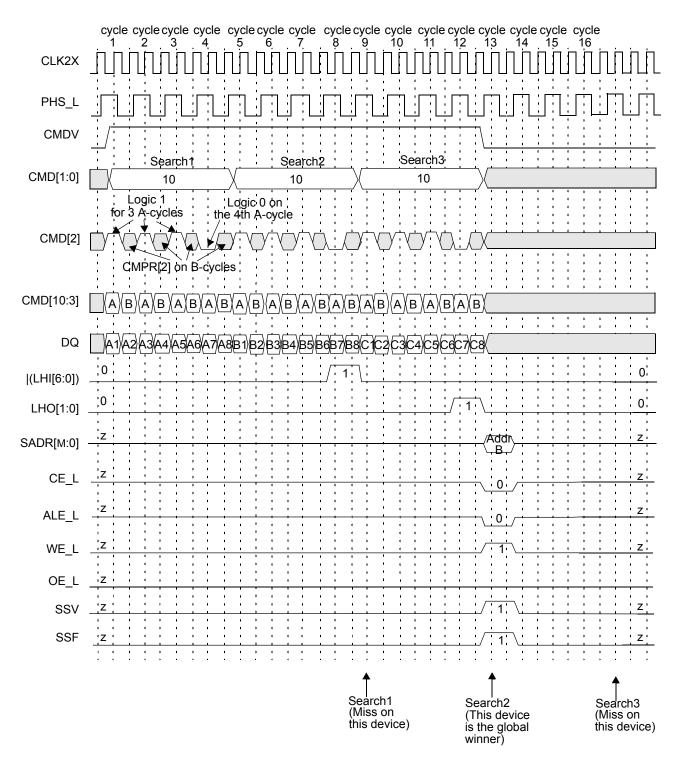

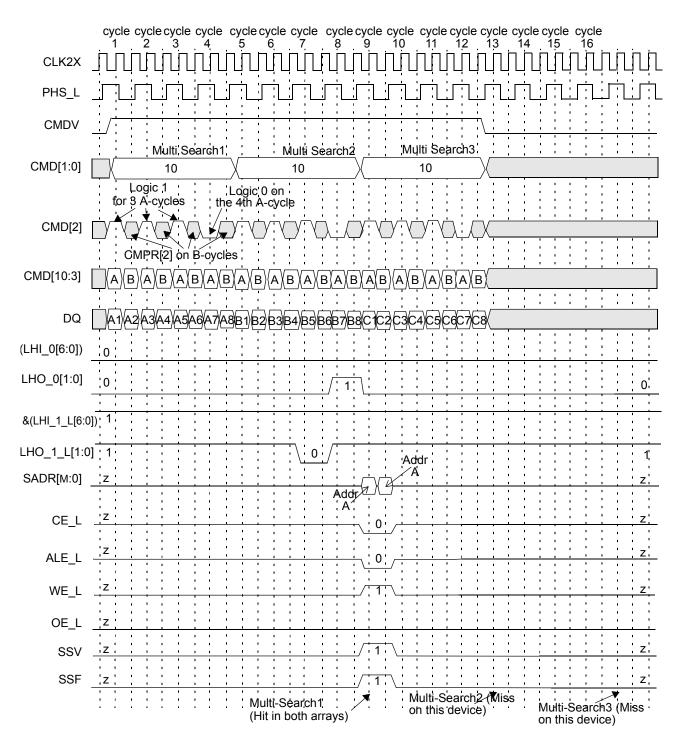

| Figure 6-35. | Timing Diagram for 576-bit MultiSearch Device Number 0                      | 91    |

| Figure 6-36. | Timing Diagram for 576-bit MultiSearch Device Number 1                      | 92    |

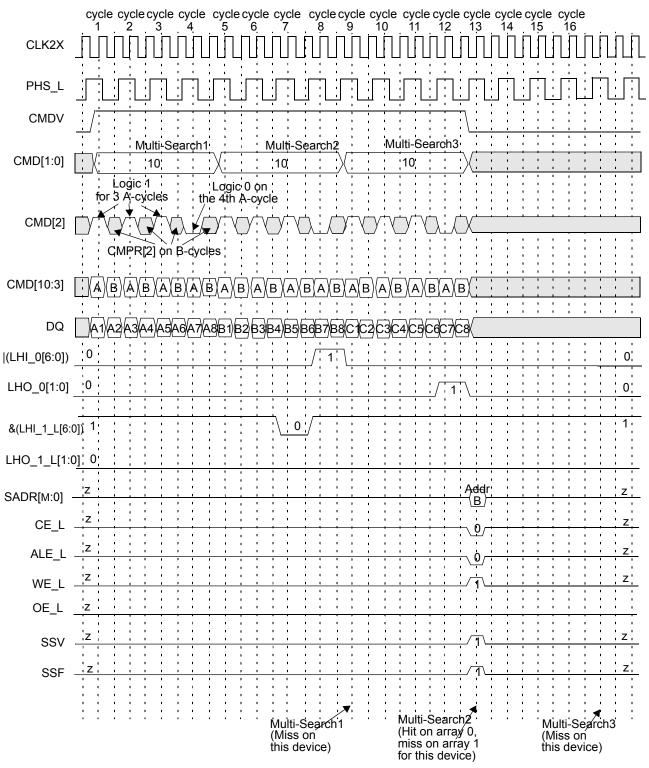

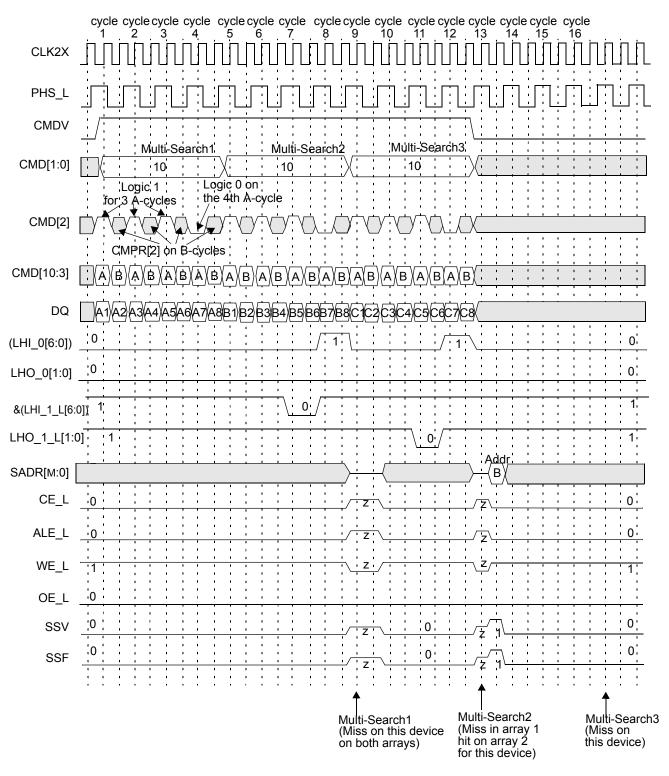

|              | Timing Diagram for 576-bit MultiSearch Device Number 7 (Last Device)        |       |

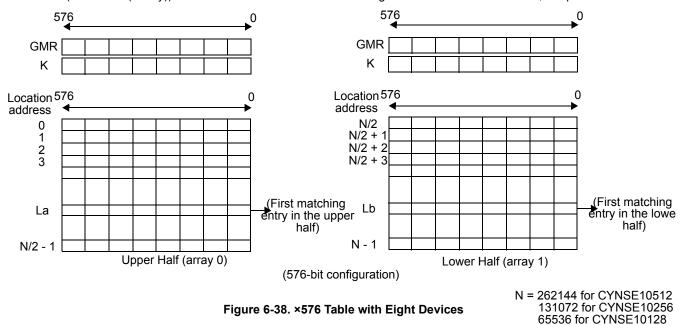

|              | ×576 Table with Eight Devices                                               |       |

|              | Multiwidth Configurations Example with CYNSE10512s                          |       |

|              | Timing Diagram for Mixed Search for Devices Above Block 0 Winning Device    |       |

| •            | Timing Diagram for Mixed Search for Block 0 Winning Device                  |       |

|              | Timing Diagram for Mixed Search for Devices Below Block 0 Winning Device    |       |

| Figure 6-43. | Timing Diagram for Mixed Search Above Block 1 Winning Device                | 99    |

| Figure 6-44. | Timing Diagram for Mixed Search for Block 1 Winning Device                  | . 100 |

| Figure 6-45. | Timing Diagram for Mixed Search Below Block 1 Winning Device                | . 101 |

| Figure 6-46. | Timing Diagram for Mixed Search Above Block 2 Winning Device                | 102   |

| Figure 6-47. | Timing Diagram for Mixed Search for Block 2 Winning Device                  | . 103 |

| Figure 6-48. | Timing Diagram for Mixed Search Below Block 2 Winning Device                | . 104 |

| Figure 6-49. | Timing Diagram for Mixed Search for All Except the Last Device in Block 3   | 105   |

| Figure 6-50. | Timing Diagram for Mixed Search for the Last Device in Block 3              | 106   |

| Figure 6-51. | Multiwidth Configurations Example for MultiSearch with CYNSE10512s          | . 107 |

| Figure 6-52. | Timing Diagram for Mixed MultiSearch (Eight Devices) for Device 0           | . 109 |

| Figure 6-53. | Timing Diagram for Mixed MultiSearch (Eight Devices) for Device 1           | . 110 |

| Figure 6-54. | Timing Diagram for Mixed MultiSearch (Eight Devices) for Device 2           | . 111 |

|              | Timing Diagram for Mixed MultiSearch (Eight Devices) for Device 7           |       |

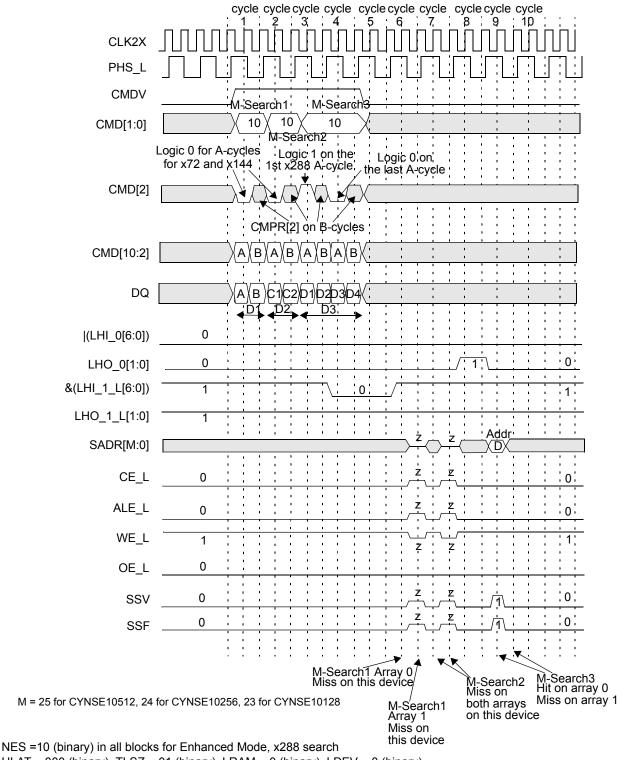

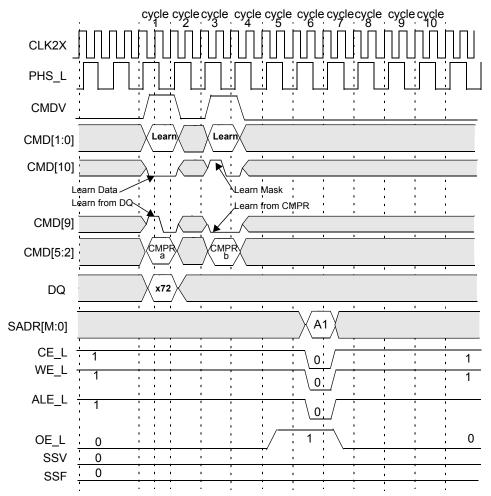

|              | Timing Diagram of 72-bit Learn from DQ Bus and CMPR Registers (One Device)  |       |

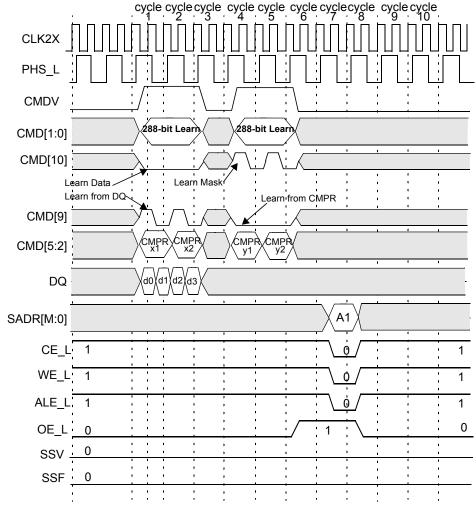

|              | Timing Diagram of 288-bit Learn from DQ Bus and CMPR Registers (One Device) |       |

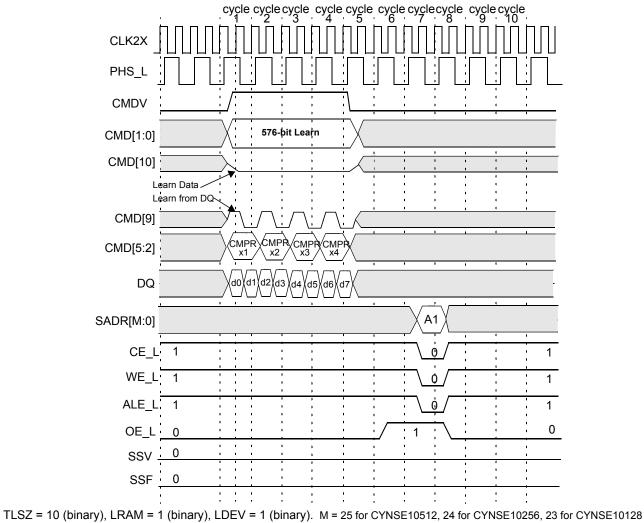

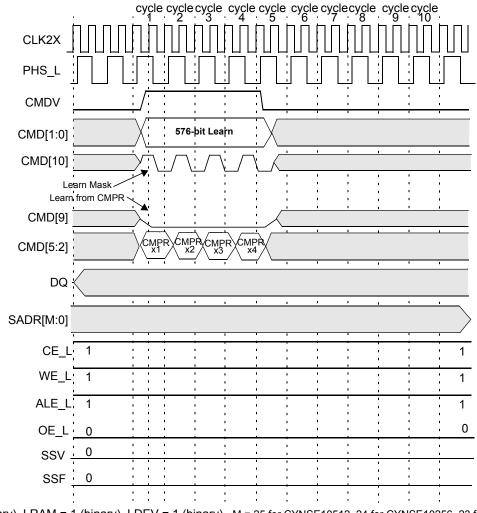

| Figure 6-58. | Timing Diagram of 576-bit Learn from DQ Bus (One Device)                    | . 116 |

# LIST OF FIGURES (continued)

| Figure 6-59. Timing Diagram of 576-bit Learn from CMPR Register (One Device)          | 117 |

|---------------------------------------------------------------------------------------|-----|

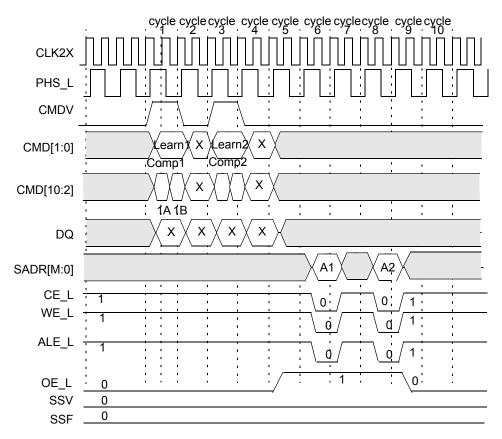

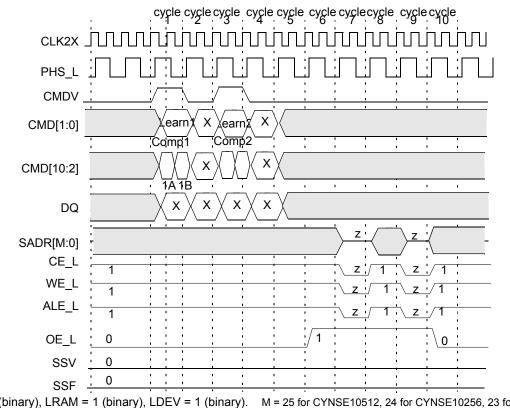

| Figure 6-60. Timing Diagram of Learn (TLSZ = 00 (binary), LDEV = 1 (binary))          |     |

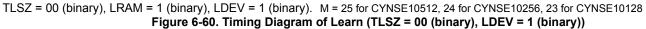

| Figure 6-61. Timing Diagram of Learn (Except on the Last Device [TLSZ = 01 (binary)]) | 119 |

| Figure 6-62. Timing Diagram of Learn on Device Number 7 (TLSZ = 01 (binary))          | 120 |

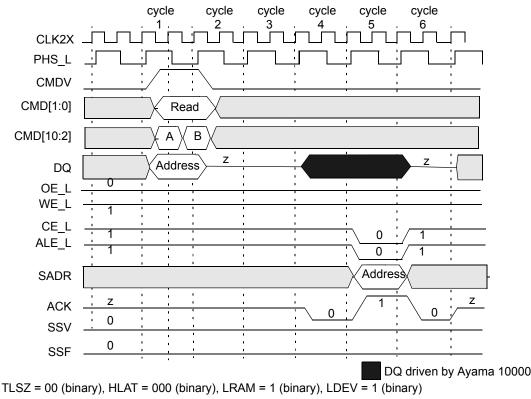

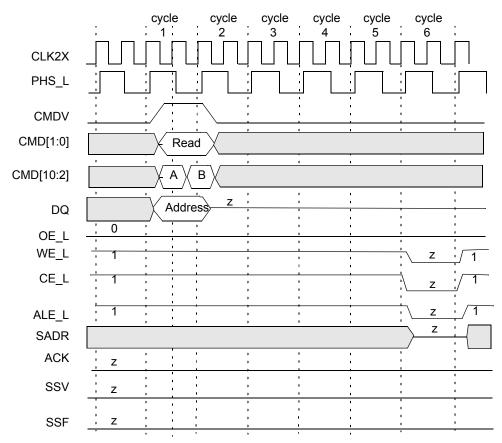

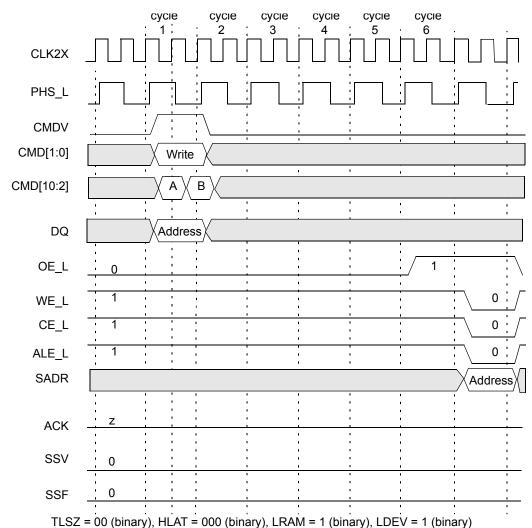

| Figure 6-63. SRAM Read Access (TLSZ = 00 (binary), HLAT = 000 (binary),               |     |

| LRAM = 1 (binary), LDEV = 1 (binary))                                                 | 122 |

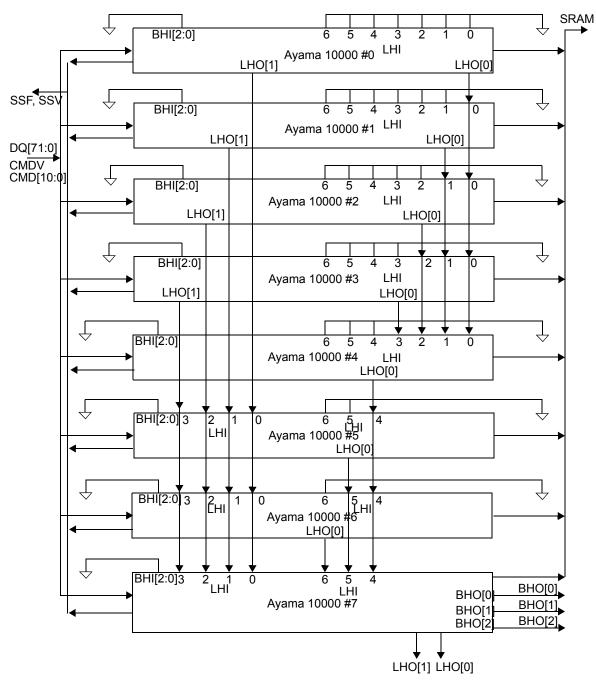

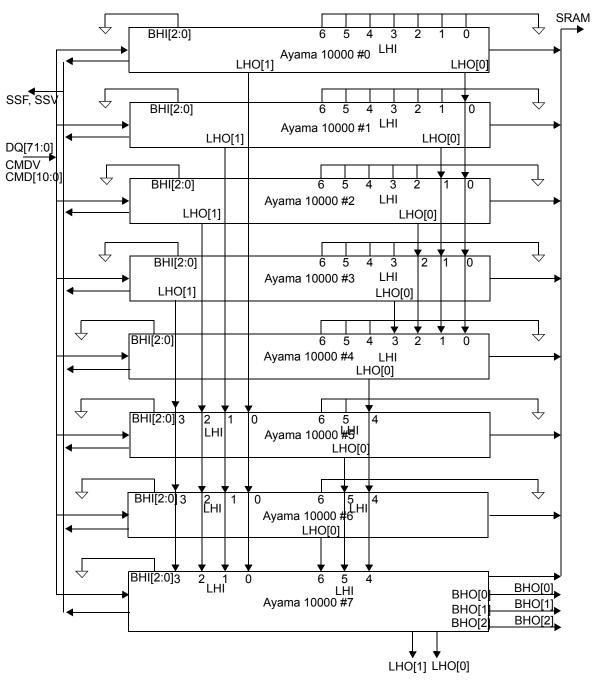

| Figure 6-64. Hardware Diagram of a Block of Eight Devices                             | 123 |

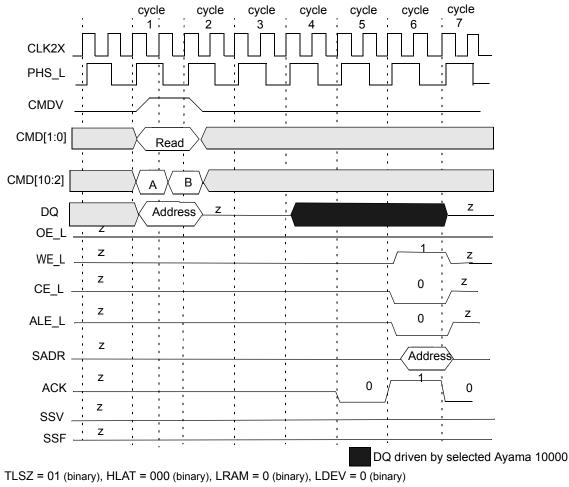

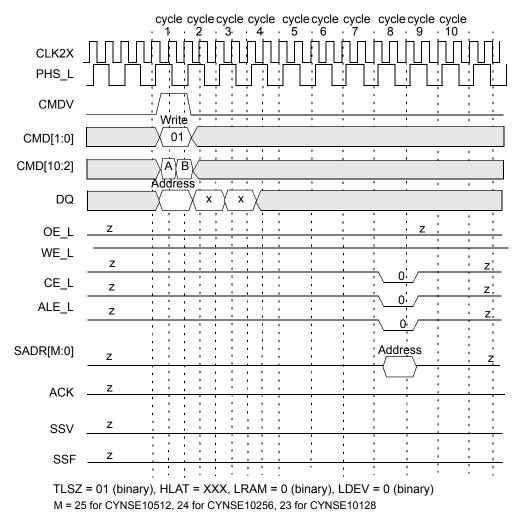

| Figure 6-65. SRAM Read of Device #0 in a Block of Eight Devices                       | 124 |

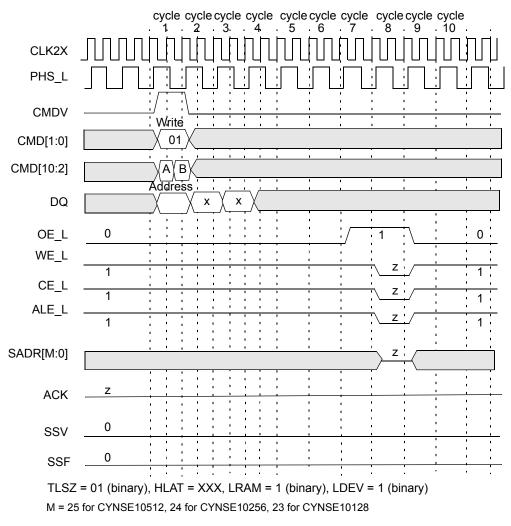

| Figure 6-66. SRAM Read Timing of Device #7 in a Block of Eight Devices                | 125 |

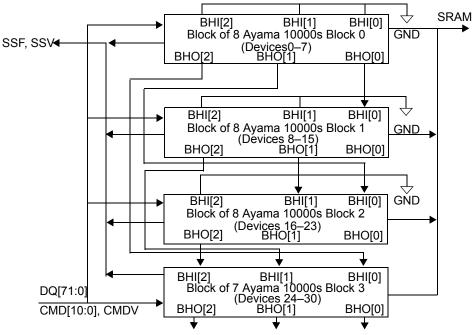

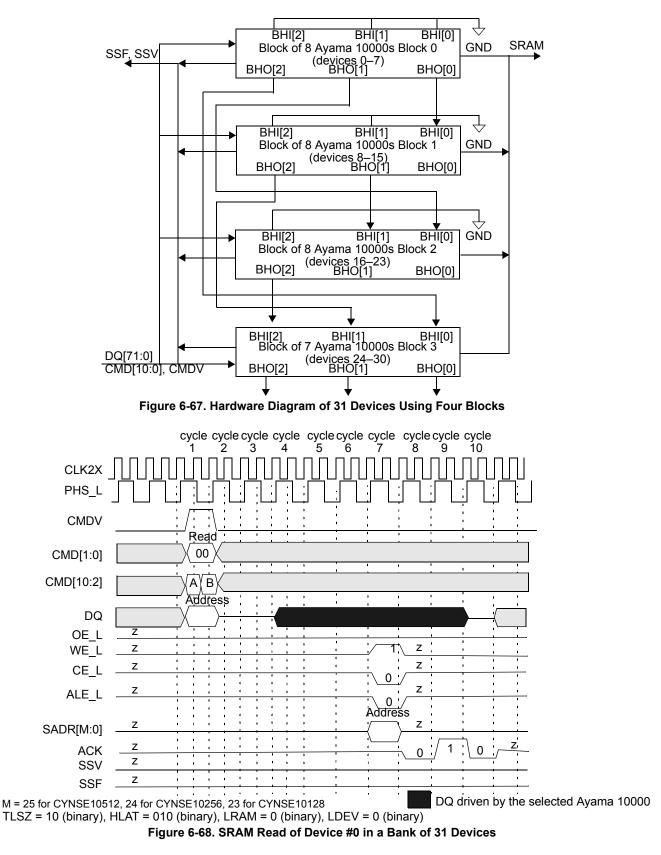

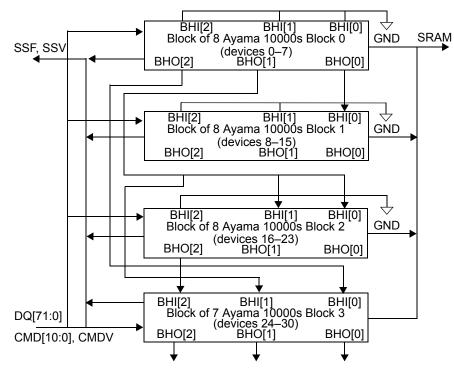

| Figure 6-67. Hardware Diagram of 31 Devices Using Four Blocks                         |     |

| Figure 6-68. SRAM Read of Device #0 in a Bank of 31 Devices                           | 126 |

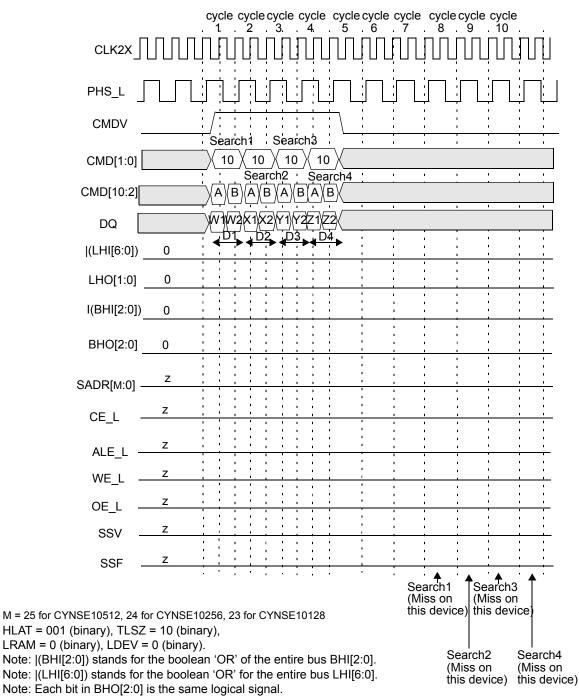

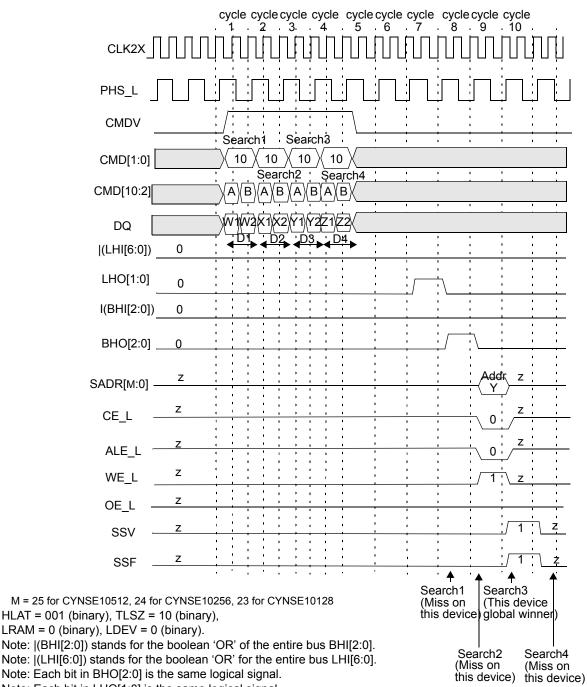

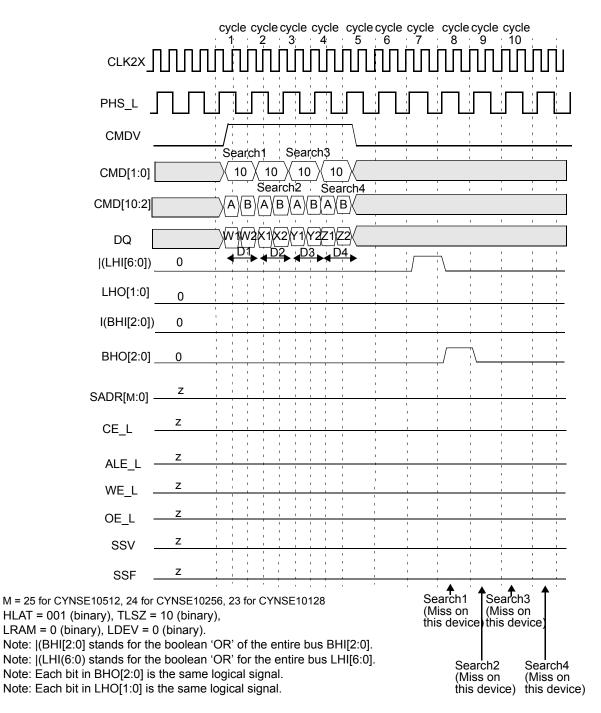

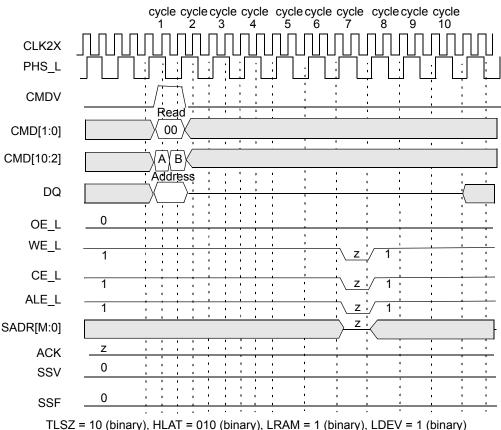

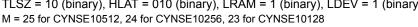

| Figure 6-69. SRAM Read of Device #0 in a Bank of 31 Devices                           | 127 |

| Figure 6-70. SRAM Write Access (TLSZ = 00 (binary), HLAT = 000 (binary),              |     |

| LRAM = 1 (binary), LDEV = 1 (binary))                                                 | 128 |

| Figure 6-71. Hardware Diagram of a Block of Eight Devices                             | 129 |

| Figure 6-72. SRAM Write of Device #0 in a Block of Eight Devices                      | 130 |

| Figure 6-73. SRAM Write Timing of Device #7 in Block of Eight Devices                 |     |

| Figure 6-74. Table of 31 Devices (Four Blocks)                                        | 132 |

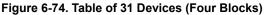

| Figure 6-75. SRAM Write of Device #0 in Bank of 31 Devices                            | 132 |

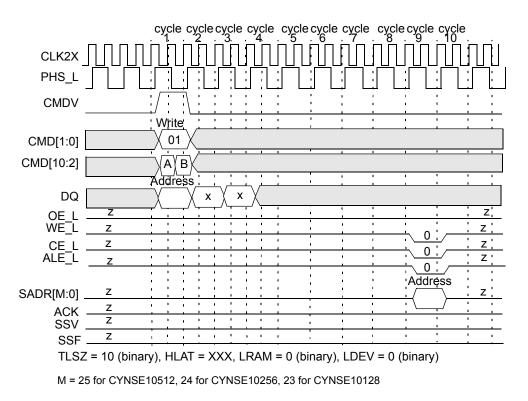

| Figure 6-76. SRAM Write Through Device #30 in Bank of 31 Devices                      | 133 |

| Figure 6-77. Timing Diagram for Full Signal (TLSZ = 10)                               | 134 |

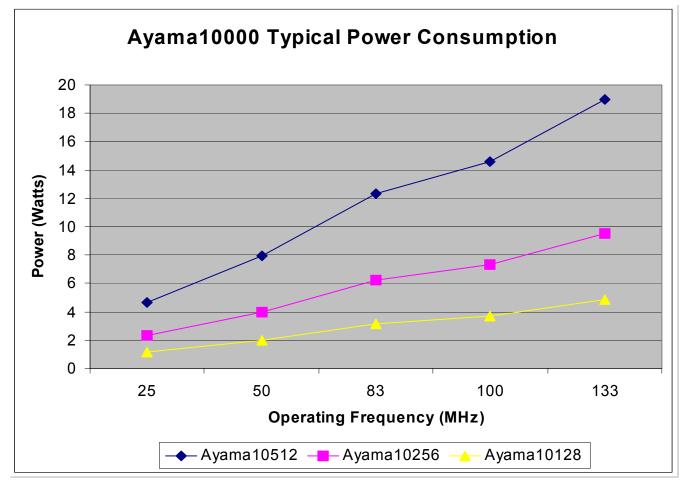

| Figure 8-1. Typical Power Consumption of Ayama 10000                                  | 136 |

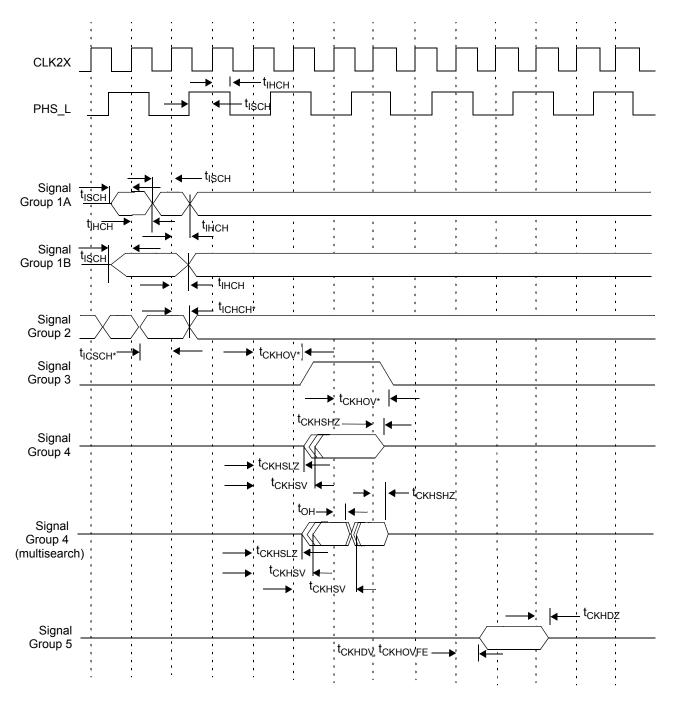

| Figure 10-1. AC Timing Wave Forms with CLK2X                                          |     |

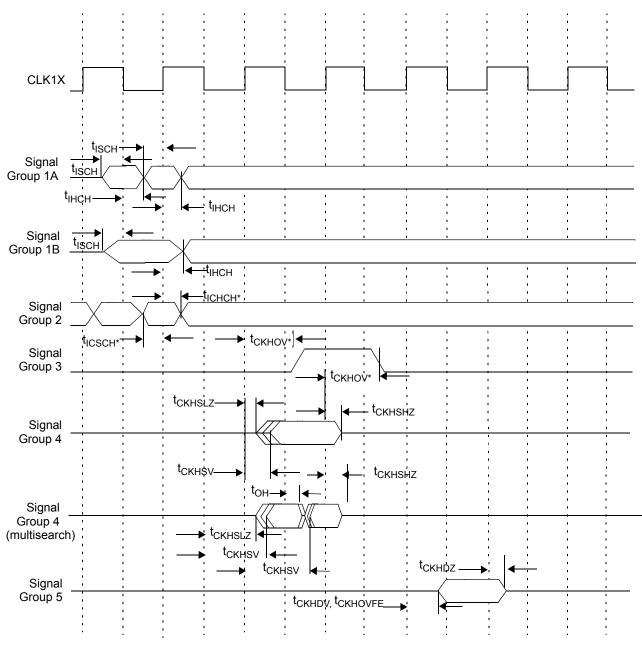

| Figure 10-2. AC Timing Wave Forms with CLK1X                                          |     |

| Figure 10-3. LVCMOS I/O Input Waveform                                                |     |

| Figure 10-4. Test Condition of 2.5V LVCMOS I/O Output Load Equivalent                 |     |

| Figure 10-5. Test Condition of 2.5V High-Z LVCMOS I/O Output Load Equivalent          |     |

| Figure 10-6. Test Condition of 1.8V High-Z LVCMOS I/O Output Load Equivalent          |     |

| Figure 10-7. HSTL I/II I/O Input Waveform                                             |     |

| Figure 10-8. Test Condition of HSTL I I/O Output Load Equivalent                      | 144 |

| Figure 10-9. Test Condition of HSTL II I/O Output Load Equivalent                     | 144 |

| Figure 10-10. Test Condition of HSTLI/II I/O High-Z Output Load Equivalent            |     |

| Figure 11-1. Pinout Diagram (Top View)                                                | 145 |

# LIST OF TABLES

| Table 3-1. Bit Position Match                                                                                                              | 1      |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Table 3-1. Bit Position Match                                                                                                              |        |

| Table 4-1. Aydilla <sup>th</sup> 10000 Sigilal Description                                                                                 | )<br>> |

| Table 5-1. Summary of Non-Enhanced and Enhanced Mode Features and Functions Differences 18                                                 | 5<br>5 |

| Table 5-2. Selection of Search Key, GMR, and CMPR in MultiSearch Operation       23         Table 5-2. List of laternal Deviators       23 |        |

| Table 5-3. List of Internal Registers                                                                                                      |        |

| Table 5-4. Search Successful Register Description   28                                                                                     |        |

| Table 5-5. Command Register Description    28                                                                                              |        |

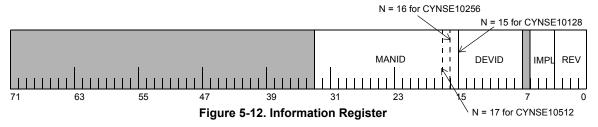

| Table 5-6. Information Register Description    30                                                                                          |        |

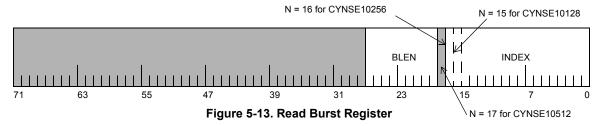

| Table 5-7. Read Burst Register Description    30                                                                                           |        |

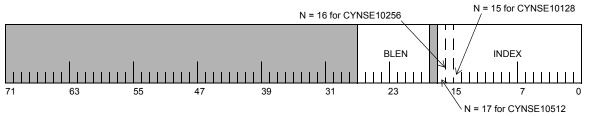

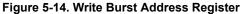

| Table 5-8. Write Burst Register Description    31                                                                                          |        |

| Table 5-9. NFA Register Description                                                                                                        |        |

| Table 5-10. Configuration Register Description    32                                                                                       |        |

| Table 5-11. Hardware Register Description    33                                                                                            | 3      |

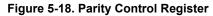

| Table 5-12. Parity Control Register Description    34                                                                                      | ł      |

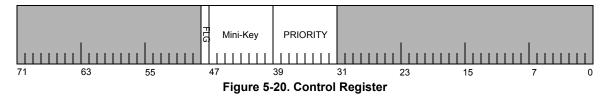

| Table 5-13. Control Register                                                                                                               |        |

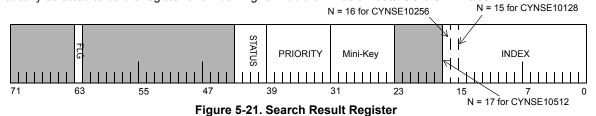

| Table 5-14. Search Result Register                                                                                                         | 3      |

| Table 5-15. SRR's INDEX Composition Based on STATUS                                                                                        |        |

| Table 5-16. Block Mini-Key Register Description                                                                                            |        |

| Table 5-17. Block Priority Register Description                                                                                            |        |

| Table 5-18. Block Parity Register Description    39                                                                                        |        |

| Table 5-19. Block NFA Register Description                                                                                                 |        |

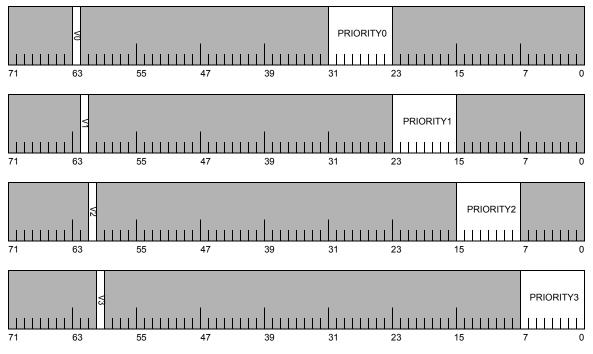

| Table 5-20. Block Priority Register Alias for Priority #0 Fields       41                                                                  |        |

| Table 5-21. Block Priority Register Alias for Priority #1 Fields                                                                           |        |

| Table 5-22. Block Priority Register Alias for Priority #2 Fields                                                                           |        |

| Table 5-23. Block Priority Register Alias for Priority #3 Fields                                                                           |        |

| Table 5-24. Pipeline Stages and Maximum Operating Speed.                                                                                   |        |

| Table 5-25. Data Array, Mask Array and External SRAM Address Space Encoding                                                                |        |

| Table 5-26. SRAM Address Generation                                                                                                        |        |

| Table 5-20. Strain Address Generation                                                                                                      |        |

|                                                                                                                                            |        |

| Table 5-28. Cascadability of Operations and Features       45         Table 6.1. Command Codes       50                                    |        |

| Table 6-1. Command Codes       50         Table 6-2. Single /Durat Dood       51                                                           |        |

| Table 6-2. Single/Burst Read Command Parameters       51         Table 6-2. Single/Burst Write Command Parameters       54                 |        |

| Table 6-3. Single/Burst Write Command Parameters       54         Table 6-4. The ST(4:0) Description       56                              |        |

| Table 6-4. TLSZ[1:0] Description       56         Table 6.5. Obj(for f 0.05) (from 0.000)       56                                         |        |

| Table 6-5. Shift of SSF and SSV from SADR       58         Table 6-6. Lit/Miss Assumptions       64                                        |        |

| Table 6-6. Hit/Miss Assumptions                                                                                                            |        |

| Table 6-7. Hit/Miss Assumption for MultiSearch Mode    67                                                                                  |        |

| Table 6-8. Hit/Miss Assumptions                                                                                                            |        |

| Table 6-9. Hit/Miss Assumptions                                                                                                            |        |

| Table 6-10. Hit/Miss Assumptions for 576-bit Multi Search    90                                                                            |        |

| Table 6-11. Hit/Miss Assumptions   95                                                                                                      |        |

| Table 6-12. Hit/Miss Assumptions in MultiSearchMode                                                                                        |        |

| Table 6-13. SRAM Write Cycle Latency from Second Cycle of Learn Instruction                                                                |        |

| Table 6-14. Required Idle Cycles Between Commands                                                                                          |        |

| Table 7-1. Supported Operations                                                                                                            |        |

| Table 7-2. TAP Device ID Register                                                                                                          | 5      |

| Table 9-1. DC Electrical Characteristics for Ayama 10000                                                                                   | 7      |

| Table 9-2. Operating Conditions for Ayama 10000                                                                                            | 1      |

| Table 10-1. AC Timing Parameters with CLK2X                                                                                                |        |

# LIST OF TABLES (continued)

| Table 10-2. AC Timing Parameters with CLK1X                               | . 140 |

|---------------------------------------------------------------------------|-------|

| Table 10-3. JTAG Timing Parameters                                        |       |

| Table 10-4. 2.5V / 1.8V AC Table for LVCMOS Test Condition of Ayama 10000 |       |

| Table 10-5. 1.5V AC Table for HSTL Test Condition of Ayama 10000          | . 144 |

| Table 11-1. Pin Assignment                                                | . 146 |

| Table 13-1. Ordering Information                                          | . 151 |

# 1.0 Features

- Up to 512K 36-bit entries in a single device for CYNSE10512

- -256K entries in 72-bit configuration

- 128K entries in 144-bit configuration

- 64K entries in 288-bit configuration

- 32K entries in 576-bit configuration

- •Up to 256K 36-bit entries in a single device for CYNSE10256

- 128K entries in 72-bit configuration

- 64K entries in 144-bit configuration

- 32K entries in 288-bit configuration

- 16K entries in 576-bit configuration

- •Up to 128K 36-bit entries in a single device for CYNSE10128

- 64K entries in 72-bit configuration

- 32K entries in 144-bit configuration

- 16K entries in 288-bit configuration

- -8K entries in 576-bit configuration

- Multiple width tables in a single device

- Single-cycle Search operation on 72-/144-bit tables

- Mini-Key™-programmable search key for fine grain table selection and power conservation

- Prioritized blocks with no overhead in table management using programmable Soft Priority™

- Parity support for reliable operation

- Non-Enhanced Mode and Enhanced Mode operation

- Up to 133 million searches per second in 72-/144-bit configuration

- Up to 66.5 million searches per second in 36-/288-bit configuration

- Up to 33.25 million searches per second in 576-bit configuration (Enhanced Mode Only)

- Enhanced Mode with MultiSearch<sup>™</sup> operation

- Up to 266 million searches per second in 72-/144-bit configuration

- Up to 133 million searches per second in 36-/288-bit configuration

- Up to 66.5 million searches per second in 576-bit configuration

- Cascadable for depth expansion

- Glueless interface to industry-standard SRAMs and SSRAMs

- Simple hardware instruction interface

- IEEE 1149.1 test access port

- 1.2V core voltage supply

- Supports 1.5V HSTL and 1.8V/2.5V LVCMOS I/O Standards

- 388-pin BGA package

# 2.0 Overview

Cypress Semiconductor Corporation's (Cypress's) Ayama<sup>™</sup> 10000 Network Search Engine (NSE) is designed to be a highperformance, pipelined, synchronous, 512K/256K/128K 36-bit entries NSE. This high-speed, high-capacity Ayama 10000 NSE can be deployed in a variety of networking and communications applications. It can be used to accelerate network protocols such as Longest-Prefix Match (CIDR), ARP, MPLS, and other layer 2, 3, and 4 protocols. The performance and features of the Ayama 10000 make it attractive in applications such as Enterprise LAN switches and routers, and broadband switching and/or routing equipment that supports multiple data rates at OC–48 and beyond. Ayama 10000 can operate at a maximum performance of 266 million searches per second (MSPS).

The Ayama 10000 is designed to be scalable in order to support network database sizes of up to 15872K 36-bit entries specifically for environments that require large network policy databases. It includes features that ease table management, reduce power consumption and improve data integrity. The device can have its features individually enabled or disabled for flexibility based on the needs of the applications. The Ayama 10000's Data and Mask arrays that make up the Core are organized into blocks that can be individually configured to optimize the device performance and provide even more flexibility.

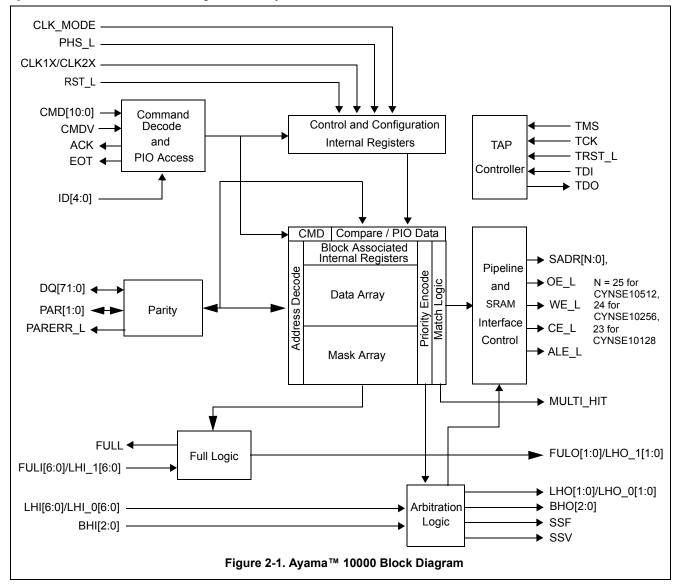

Figure 2-1 below shows the block diagram of the Ayama 10000.

# CONFIDENTIAL PRELIMINARY

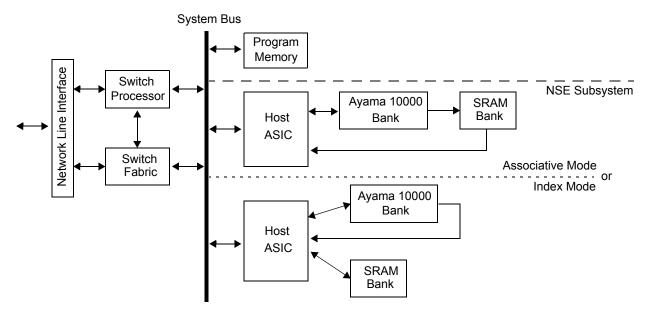

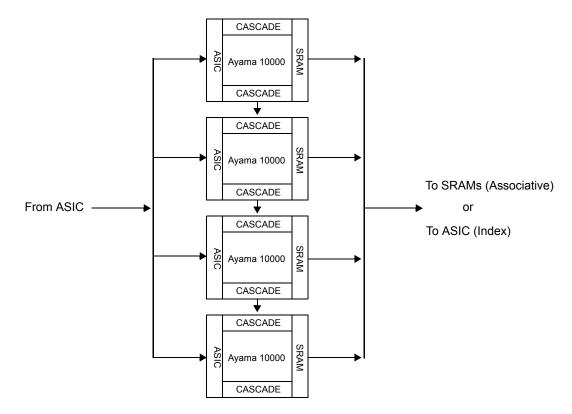

*Figure 2-2* shows how an NSE subsystem can be formed using a host ASIC, a bank of Ayama 10000 devices and a bank of SRAM devices. It presents an example of how the NSE subsystem is integrated in a switch or router. The example also shows two possible ways of connecting the devices in the NSE subsystem. In the Associative set-up, the host ASIC sends instructions to the NSE. Where applicable, the NSE drives the SRAM inputs and the SRAM then returns the requested data to the host ASIC. In the Index set-up, the NSE's SRAM address information is routed back to the host ASIC. The host ASIC then interacts with the SRAM bank after it receives the result from the NSE.

Figure 2-2. Example of Switch/Router Implementation Using Ayama 10000

# 3.0 Device Architecture Overview

## 3.1 Data Array, Mask Array and Table Widths

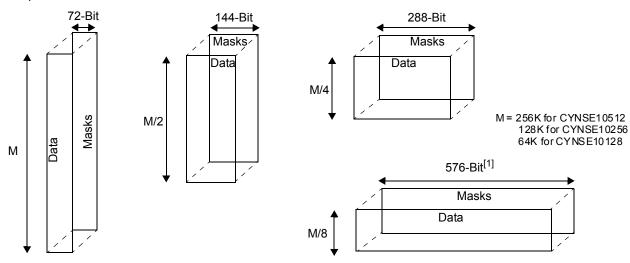

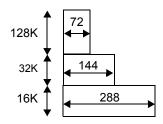

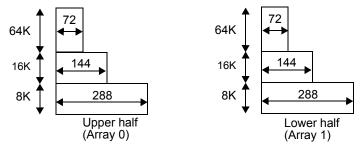

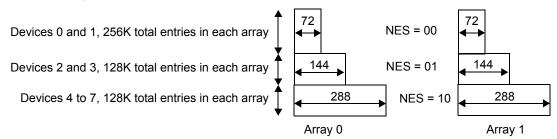

The Ayama 10000 device consists of M × 72-bit (M = 256K for CYNSE10512, 128K for CYNSE10256, 64K for CYNSE10128) storage cells referred to as data bits. There is also a mask cell corresponding to each data cell. A database entry includes both the data and mask cells. *Figure 3-1* shows the four possible table width sizes of the data and mask cells and the maximum possible table depth for each width.

Figure 3-1. Ayama 10000 Database Table Widths

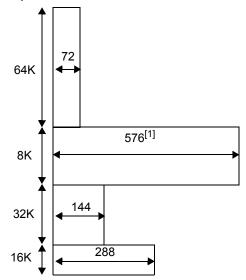

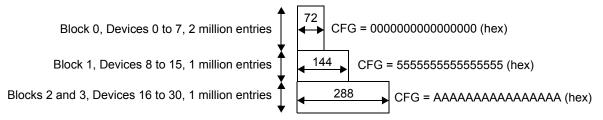

The Ayama 10000 can be configured to contain tables of different widths in one device up to a maximum equal to 512K/256K/128K 72-bit entries. For example, a single Ayama 10000 device can have both a 5-Tuple Flow table and an IPv6 forwarding table. *Figure 3-2* shows a sample configuration of multiple table widths in a CYNSE10512 device.

#### Note:

1. 576-bit table configuration is only supported in the Enhanced mode.

# 3.2 Data and Mask Addressing

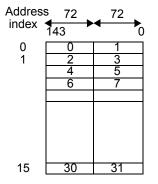

Each 72-bit entry in the device can be accessed directly through its address index. The data and mask arrays addresses are as shown in *Figure 3-3*.

Figure 3-3. Addressing the Ayama 10000 Data and Mask Arrays

## 3.3 Successful Search and Multiple Match Arbitration

During a Search operation, the search data bit is masked with the corresponding global mask bit from the selected Global Mask Register and the mask array bit before being compared to the data array entry bit to check for a match at that bit position (see *Table 3-1*). The entry with a match on every bit position results in a successful Search. For example, in order for a successful Search within a device to make the device the local winner, all 72-bit positions must generate a match for a 72-bit entry in 72-bit configured quadrants. The same applies to 144-bit, 288-bit, and 576-bit searches.

The on-chip priority encoder selects the first matching entry in the database that is nearest to memory address 0. An arbitration mechanism using a cascade bus determines the global winning device among the local winning devices in a Search cycle. The global winning device then drives the output signals. When there is no successful Search, the device designated as the last device (Refer to *Section 5.3* for more information on last device designation) will drive the output signals.

#### Table 3-1. Bit Position Match

| Global Mask Bit | Mask Array Bit | Data Array Bit | Search Key Bit | Match Result |

|-----------------|----------------|----------------|----------------|--------------|

| 0               | Х              | Х              | Х              | 1            |

| 1               | 0              | Х              | Х              | 1            |

| 1               | 1              | 0              | 0              | 1            |

| 1               | 1              | 1              | 0              | 0            |

| 1               | 1              | 0              | 1              | 0            |

| 1               | 1              | 1              | 1              | 1            |

# 4.0 Signals Description

Table 4-1 lists and describes all Ayama 10000 signals.

## Table 4-1. Ayama<sup>™</sup> 10000 Signal Description

| Parameter               | Type <sup>[2]</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clocks and Reset        |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CLK_MODE                | I                   | <b>Clock Mode</b> . Selects the clock source for the device. When set to Low, the device uses both CLK2X and PHS_L for its clock sources. When pulled High ( $V_{DDQ}$ _ASIC), the device uses CLK1X for its clock source (PHS_L must be externally grounded).                                                                                                                                                                                                                                  |

| CLK2X/CLK1X             | 1                   | Master Clock. CLK_MODE selects either the CLK2X or CLK1X as the clock input signal.         CLK1X         Input signals are sampled on both rising and falling edges.         Output signals can be driven on both falling and rising depending on the operation and the device configuration.         CLK2X         Input signals are sampled on the rising edge.         Output signals are driven on the rising edge.                                                                        |

| PHS_L                   | I                   | <b>Phase</b> . An input signal that must switch at half the frequency of CLK2X. This signal should be pulled LOW when the device is in CLK1X mode. See Section 5.6, "Clocks," on page 42.                                                                                                                                                                                                                                                                                                       |

| RST_L                   | I                   | <b>Reset</b> . Driving RST_LLOW initializes the device to the default state. The device becomes active stable 4 CLK1X (8 CLK2X) cycles after RST_L is driven High (90% threshold).                                                                                                                                                                                                                                                                                                              |

| Configuration           | 1                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CFG_L                   |                     | Configuration. When CFG_L is set to Low, the device will tristate DQ[71:68].                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ID[4:0]                 | 1                   | <b>Device Identification</b> . The binary-encoded device identification for a depth-cascaded system starts at "00000" and goes up to "11110". "11111" is reserved as the broadcast address which selects all NSEs in the cascade.<br>On a broadcast Read, only the device with the LDEV bit set to '1' will respond.                                                                                                                                                                            |

| 1010051                 |                     | Any ID bit that is to be set High must be connected to V <sub>DDQ_ASIC</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ASICSEL                 |                     | ASIC IO Select. When this signal is pulled High (1.8V or 2.5V LVCMOS), the Command,<br>Data and Cascade buses will operate in LVCMOS mode. When tied to Low, the buses<br>will operate in HSTL mode.<br>Signals affected by ASICSEL selection:<br><i>Clocks</i> : CLK2X/CLK1X, PHS_L, RST_L<br><i>Command and Data</i> : CMD[10:0], CMDV, DQ[71:0], PAR[1:0], ACK, EOT, SSF, SSV,<br>MULTI_HIT<br><i>Cascade Interface</i> : LHI[6:0], LHO[1:0], BHI[2:0], BHO[2:0], FULI[6:0], FULO[1:0], FULL |

| SRAMSEL                 | 1                   | SRAM IO Select. When this signal is pulled High (1.8V or 2.5V LVCMOS), the SRAM<br>Interface will operate in LVCMOS mode. When tied to Low, the interface will operate in<br>HSTL mode.<br>Signals affected by SRAMSEL selection:<br>SADR[25:0], CE_L, WE_L, OE_L, ALE_L                                                                                                                                                                                                                        |

| HSVREF0                 | I                   | <b>HSTL Reference Voltage</b> . When ASICSEL is set to GND, this signal must be connected to the HSTL reference voltage (VDDQ_ASIC/2). Otherwise, they should be left floating.                                                                                                                                                                                                                                                                                                                 |

| HSVREF1                 |                     | HSTL Reference Voltage. Refer to HSVREF0 description.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PARERR_L <sup>[3]</sup> | 0                   | <b>Parity Error</b> . This signal is updated when there is a Core parity error or DQ Bus parity error. It is an Active-Low Open-Drain signal that requires an external pull-up resistor to VDDQ_ASIC.<br>This signal is valid only after the device is fully initialized.                                                                                                                                                                                                                       |

| ASIC Interface / Comm   | nand and Dat        | a Buses (LVCMOS or HSTL I/II)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CMD[10:0]               |                     | <b>Command Bus</b> . Bit[10:2] contains the command parameters and Bit[1:0] specifies the command.                                                                                                                                                                                                                                                                                                                                                                                              |

# Table 4-1. Ayama<sup>™</sup> 10000 Signal Description (continued)

| Parameter                | Type <sup>[2]</sup> | Description                                                                                                                                                                                                                                                                                       |  |

|--------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CMDV                     | ļ                   | Command Valid. This signal indicates valid command in the CMD bus when set to High.                                                                                                                                                                                                               |  |

| DQ[71:0]                 | I/O                 | Address/Data Bus. This signal carries the following information:                                                                                                                                                                                                                                  |  |

|                          |                     | Search operation: Compare Data (Search Key)<br>SRAM PIO operations: SRAM Address<br>Other operations to Register, Data, and Mask Array regions: Address and Data                                                                                                                                  |  |

| PAR[1:0]                 | I/O                 | <b>Parity Bus</b> . These signals contain the even parity values for the DQ bus. On the Read return data, the NSE generates the parity bits. On all other operations these bits are externally driven. Bit [0] is the parity for all even DQ signals. Bit[1] is the parity for all od DQ signals. |  |

| ACK <sup>[4]</sup>       | Т                   | <b>Read Acknowledge</b> . This signal indicates that valid data is available on the DQ bus during register, data, and mask array Read operations, or that the data is available on the SRAM data bus during SRAM Read operations.                                                                 |  |

| EOT <sup>[4]</sup>       | Т                   | <i>End of Transfer</i> . This signal indicates the end of burst transfer to the data or mask array during Read or Write burst operations.                                                                                                                                                         |  |

| SSF <sup>[5]</sup>       | Т                   | <b>Search Successful Flag.</b> When asserted, this signal indicates that the device is the global winner in a Search operation.                                                                                                                                                                   |  |

| SSV <sup>[5]</sup>       | Т                   | <b>Search Successful Flag Valid</b> . When asserted, it indicates valid SSF value. In Enhanced mode, this signal also indicates valid FULL and MULTI_HIT values.                                                                                                                                  |  |

| MULTI_HIT <sup>[5]</sup> | 0                   | <i>Multiple Hit Flag.</i> In a Search operation, this signal indicates that there are multiple entries in the array or in the selected blocks that match the Search key when it is set to 1. In a Learn operation, it indicates that there are multiple free entries.                             |  |

|                          |                     | In Non-Enhanced mode, it becomes valid 4 CLK1X cycles after the command is issued.<br>In Enhanced mode, it becomes valid when SSV is 1.                                                                                                                                                           |  |

| FULL                     | Т                   | <i>Full Flag</i> . When High, it indicates that the table in the array or in the selected blocks (Enhanced mode) is full.                                                                                                                                                                         |  |

|                          |                     | In the Non-Enhanced mode, it becomes valid 4 CLK1X cycles after the command is issued.<br>In the Enhanced mode, it becomes valid when SSV is 1.                                                                                                                                                   |  |

| HIGH_SPEED1              | I                   | <i>High Speed 1</i> . This signal must be pulled High (V <sub>DDQ_ASIC</sub> ) when the device operates at CLK2X frequency above 166 MHz.                                                                                                                                                         |  |

| HIGH_SPEED2              | 1                   | <i>High Speed 2</i> . This signal must be pulled High (V <sub>DDQ_ASIC</sub> ) when the device operates at CLK2X frequency above 200 MHz.                                                                                                                                                         |  |

| SRAM Interface (LVC      | MOS or HSTL         | I/II)                                                                                                                                                                                                                                                                                             |  |

| SADR[M:0] <sup>[5]</sup> | Т                   | <b>SRAM Address</b> . This bus contains address lines to access off-chip SRAMs that contain associative data. In a cascaded system of multiple Ayama 10000 NSEs, each corresponding SADR bit from all cascaded devices must be tied together.                                                     |  |

|                          |                     | M = 25 for CYNSE10512, 24 for CYNSE10256, 23 for CYNSE10128.                                                                                                                                                                                                                                      |  |

| CE_L <sup>[5]</sup>      | Т                   | <b>SRAM Chip Enable</b> . This is the chip enable (CE) control for external SRAMs. In a cascaded system of multiple Ayama 10000 NSEs, CE_L of all cascaded devices must be tied together. This signal is then driven by only one of the devices.                                                  |  |

| WE_L <sup>[5]</sup>      | Т                   | <b>SRAM Write Enable</b> . This is the Write enable control for external SRAMs. In a cascaded system of multiple Ayama 10000 NSEs, WE_L of all cascaded devices must be tied together. This signal is then driven by only one of the devices.                                                     |  |

| OE_L <sup>[5]</sup>      | Т                   | <b>SRAM Output Enable</b> . This is the output enable (OE) control for external SRAMs. Only the last device drives this signal (the device that has the LRAM bit set).                                                                                                                            |  |

| ALE_L <sup>[5]</sup>     | Т                   | <b>Address Latch Enable</b> . When this signal is Low, the addresses are valid on the SRAM address bus. In a cascaded system of multiple Ayama 10000s, the ALE_L of all cascaded devices must be tied together. This signal is then driven by only one of the devices.                            |  |

## Table 4-1. Ayama<sup>™</sup> 10000 Signal Description (continued)

| Parameter                         | Type <sup>[2]</sup> | [2] Description                                                                                                                                                                                        |  |

|-----------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Cascade Interface (LVCI           | MOS and H           | STL)                                                                                                                                                                                                   |  |

| LHI[6:0]<br>LHI_0[6:0] (MSE=1)    | I                   | <b>Local Hit In/Local Hit In Array 0</b> . These signals are inputs from upstream devices in a cascade that indicate whether there is a hit in the upstream/previous device(s).                        |  |

|                                   |                     | When MultiSearch is performed, LHI[6:0] becomes LHI_0[6:0] (Local Hit input signals for Array 0).                                                                                                      |  |

| LHO[1:0]<br>LHO_0[1:0] (MSE=1)    | 0                   | <b>Local Hit Out/ Local Hit Out Array 0</b> . LHO[1] and LHO[0] are logically the same signal.<br>One of these signal is connected to one input on the LHI bus of the downstream devices in a cascade. |  |

|                                   |                     | When MultiSearch is performed, LHO[1:0] becomes LHO_0[1:0] (Local Hit output signals for Array 0).                                                                                                     |  |

| BHI[2:0]                          | I                   | <b>Block Hit In</b> . These signals are inputs from the last device in the upstream blocks in a cascade that indicate whether there is a hit in the upstream/previous block(s).                        |  |

| BHO[2:0]                          | 0                   | <b>Block Hit Out</b> . These signals are logically the same signal. One of these signals is connected to one input on the BHI bus of the downstream devices in the downstream blocks.                  |  |

| FULI[6:0]                         | I                   | <i>Full In/Local Hit In Array 1</i> . Each signal is driven by an upstream device's FULO output in a block to generate the FULL signal for that block. During a Search operation, these                |  |

| LHI_1_L[6:0] (MSE=1)              |                     | signals indicate whether an upstream device had a free entry for a future Learn.                                                                                                                       |  |

|                                   |                     | When MultiSearch is performed, FULI[6:0] becomes active Low LHI_1_L[6:0] (Local Hit input signals for Array 1).                                                                                        |  |

| FULO[1:0]<br>LHO_1_L[1:0] (MSE=1) | 0                   | <i>Full Out/Local Hit Out Array 1</i> . FULO[0] and FULO[1] are logically the same signal. One of these signal is connected to one input on the FULO bus of the downstream devices in a cascade.       |  |

|                                   |                     | When MultiSearch is performed, FULO[1:0] becomes active Low LHI_0_L[1:0] (Local Hit output signals for Array 1).                                                                                       |  |

| Supplies                          | •                   | •                                                                                                                                                                                                      |  |

| V <sub>DD</sub>                   |                     | Core Supply: 1.2V.                                                                                                                                                                                     |  |

| V <sub>DD_PLL</sub>               |                     | PLL Block Supply: 1.2V.                                                                                                                                                                                |  |

| V <sub>DDQ_ASIC</sub>             |                     | ASIC and Cascade Interface I/O Supply: 1.5V (HSTL) or 1.8V/2.5V (LVCMOS).                                                                                                                              |  |

| V <sub>DDQ_SRAM</sub>             |                     | SRAM Interfaced I/O Supply: 1.5V (HSTL) or 1.8V/2.5V (LVCMOS).                                                                                                                                         |  |

| V <sub>DDQ_JTAG</sub>             |                     | JTAG Test Access Port I/O Supply: 2.5V (LVCMOS).                                                                                                                                                       |  |

| Test Access Port                  |                     |                                                                                                                                                                                                        |  |

| TDI                               | I                   | Test access port test data in.                                                                                                                                                                         |  |

| ТСК                               | I                   | Test access port test clock.                                                                                                                                                                           |  |

| TDO                               | Т                   | Test access port test data out.                                                                                                                                                                        |  |

| TMS                               | I                   | Test access port test mode select.                                                                                                                                                                     |  |

| TRST_L                            | I                   | Test access port reset.                                                                                                                                                                                |  |

Notes:

2

I = Input only, I/O = input or output, O = output only, T = three-state output. The rise time of PARERR\_L will depend on the value of the pull-up resistance. Sufficient delay should be allotted for in the error routine after clearing the parity error in the parity control register and before this pin is sampled as part of the next command. Recommended external pull-up resistance range:  $4.7K\Omega$  to  $47K\Omega$ . 3. 4. Require an external pull-down resistor such as  $47K\Omega$  or  $100K\Omega$ .

These signals will output at the rising edge of CLK2X (both rising and falling edges of CLK1X) in a MultiSearch operation. 5.

# 5.0 Functional Description

## 5.1 Modes of Operation

Ayama 10000 can operate in two different modes of operation: Non-Enhanced and Enhanced. The Non-Enhanced mode of operation is provided for backward compatibility with the CYNSE70000 device family. The Enhanced mode allows the Ayama 10000 to utilize the features that can be used to lower power consumption, ease table management, increase data integrity and increase Search throughput. These features are Mini-Key<sup>™</sup>, Soft Priority<sup>™</sup>, Parity, and MultiSearch<sup>™</sup>. The following subsections provide more information on each of the modes and features.

The device powers-up in Non-Enhanced mode. A switch to Enhanced mode and activation of the features require the user to configure internal registers with appropriate values. Refer to *Section 5.4* for detailed information on the internal registers.

Table 5-1 lists the features and functions that are different between the two modes of operation.

| Features/Functions                 | Non-Enhanced                                                                         | Enhanced                                                                                      |

|------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Maximum Search Throughput          | 133 MSPS                                                                             | 266 MSPS                                                                                      |

| MultiSearch™                       | No                                                                                   | Yes                                                                                           |

| Soft Priority™                     | No                                                                                   | Yes                                                                                           |

| Mini-Key™                          | No                                                                                   | Yes                                                                                           |

| Parity                             | No                                                                                   | Yes                                                                                           |

| Learn Operation                    | Data from CMPR Register;<br>Target Data Array;<br>Supports x72 and x144 table widths | Data from CMPR Register or DQ Bus;<br>Target Data or Mask Array;<br>Supports all table widths |

| Where to Configure the Table Width | CONFIG Register                                                                      | BMR Register                                                                                  |

| Table Widths Supported             | x72, x144, x288                                                                      | x72, x144, x288, x576                                                                         |

| Data and Mask Array Organization   | 32/16/8 8Kx72-bit Partitions for<br>CYNSE10512/256/128 respectively                  | 128/64/32 2Kx72-bit Blocks for<br>CYNSE10512/256/128 respectively                             |

## 5.1.1 Non-Enhanced Mode

In the Non-Enhanced mode of operation, the Ayama 10000 device is organized into 32/16/8 partitions (corresponds to CYNSE10512/256/128, respectively) that each can be configured to be 8K x 72, 4K x 144, or 2K x 288. The 576-bit table width configuration is not supported in this operation mode. The LSB of each 72-bit is designated to indicate whether that entry is used or not. When the entry is empty, that bit must be set to 0. When the entry is used, that bit must be set to 1. For example, in a 288-bit table a used entry will have bit[0], bit[72], bit[144], and bit[216] set to 1. When all bit[0] are set to 1, the Ayama 10000 will assert FULO[1:0] to "11."

References are present throughout this document to indicates features that are applicable when device is in this mode.

Internal registers for configuration: CONFIG and CMD.

#### 5.1.2 Enhanced Mode

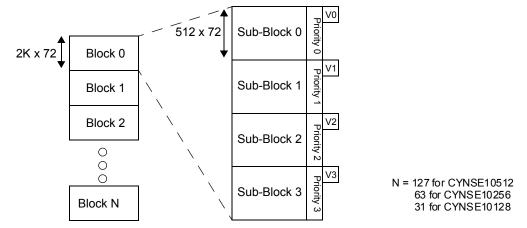

In Enhanced mode, Ayama 10000 is organized into 128/64/32 blocks (corresponds to CYNSE10512/256/128 respectively) of 2K x 72 which can also be configured into 1K x 144, 512 x 288, or 256 x 576. The Mini-Key, Soft Priority, Parity, and MultiSearch features can also be activated. Each block has internal block registers associated to it that needs to be initialized before the device goes into normal operation. *Figure 5-1* shows the general overview of the block registers association.

References are present throughout this document to indicates features that are applicable when the device is in this mode.

# CONFIDENTIAL PRELIMINARY

Figure 5-1. Blocks and Block Registers Association

#### 5.1.2.1 Mini-Key

The Mini-Key feature allows the device to power down blocks within the device that are not being selected to participate in the search operation. This results in lower power consumption. When a device has multiple tables, the block architecture of the device combined with Mini-Key can be used to ease table expansion or reorganization. There are four Mini-Keys that can be associated with each block (*Figure 5-2*) which supports each block to be a member of up to four logical tables. The block register that holds the Mini-Key values also includes the field that configures the block to be of a certain table width.

Figure 5-2. Mini-Key Register Contents

During a Search operation, the Search key width as well as the Search Mini-Key are used to selectively activate certain blocks. A block will participate in the Search operation only when the Search width matches the block's table width and the Search Mini-Key matches one of the four Mini-Keys of the block.

Internal registers for configuration: CMD, CPR and BMR.

#### 5.1.2.2 Soft Priority

Table management can become a time consuming process and slow down the performance of the system. In an edge router with multiple table of same widths in one or more Ayama 10000 devices, that constantly update the entries, one table may become full very quickly. The time it takes to process table expansion and data reorganization can be critical in a system that requires high performance and quality of service. Soft Priority feature in the Ayama 10000 can help avoid that problem. For Soft Priority purposes, each 2Kx72 block of Data/Mask array is arranged into four 512 x 72 sub-blocks. Each sub-block has a user-program-

Page 19 of 153

mable Soft Priority value that becomes part of the search key when Soft Priority feature is enabled. This feature eases the management of the tables, especially for table expansion. Each sub-block also has a Priority Valid bit that can be used to set the Soft Priority value of the sub-block to invalid state which will also prevent the sub-block from participating in a search operation.

Figure 5-3 shows the associations of the sub-blocks and Soft Priority.

Figure 5-3. Sub-Blocks and Soft Priority Associations

Internal registers for configuration: CMD, CPR and BPR.

#### 5.1.2.3 Parity

Ayama 10000 introduces parity to provide additional protection for data integrity. Parity checking can be performed both on the data transmission that passes through DQ bus and the data stored in the Core (data and mask arrays). The Parity feature can be enabled through the PARITY register. DQ Bus and Core parity checking can be independently enabled. When parity checking is enabled, a Write operation ignores any masking and all bits are written as presented in the DQ bus.

Even Parity is used in the parity checking. For example, if there is an odd number of logic-1 bits in a word, the corresponding parity bit will be set High in order for the combination (word and parity bit) to have even parity.

When an error is detected, the device will update the PARITY register and set the parity error flag (PARER\_L) to report the error. Parity status is not cascaded. However, PARERR\_L is an open-drain signal to allow signals from cascaded Ayama 10000 devices to be connected together and provide cascaded parity error detection. Therefore, the AC timing parameters associated with the signal (rise time/fall time) will be dependent on the loading conditions. Note that all parity status fields in PARITY and BPAR registers needs to be cleared by the ASIC after fixing the errors.

Internal registers for configuration: PARITY and BPAR.

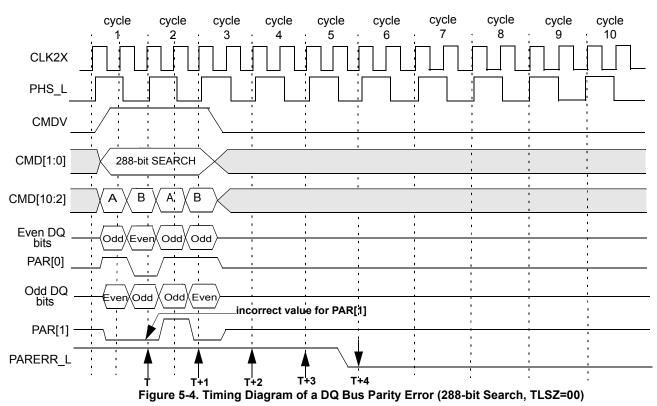

#### DQ Bus Parity

The DQ bus is divided into even-bits and odd-bits groups for parity checking. Parity bits of both even- and odd-bits groups are provided in the bidirectional PAR[1:0]. When the ASIC is driving the DQ bus, the ASIC must generate the parity bits. When the NSE is driving the DQ bus, the NSE will generate the parity bits.

When the ASIC is driving the DQ bus, the NSE will calculate the data stream parity and compare it to PAR[1:0]. When there is an error, the NSE will update the PARITY register and set PARERR\_L to 0. PARERR\_L is valid on the  $(3+T)^{th}$  cycle of latency for a Read operation and  $(4+T)^{th}$  cycle of latency for the other operations. T is the cycle where the bus parity error is detected. When a DQ bus parity error is detected, the NSE must be reset and reinitialized.

*Figure 5.4* shows the timing diagram of a DQ Bus Parity error during a 288-bit Search instruction. In cycle 1B the parity of the odd DQ bits is shown to be '1' while the corresponding parity bit (PAR[1]) is '0' (should be High for parity check to result in a '0'). The PARERR\_L signal goes Low 4 cycles after the error is detected.

# CONFIDENTIAL PRELIMINARY

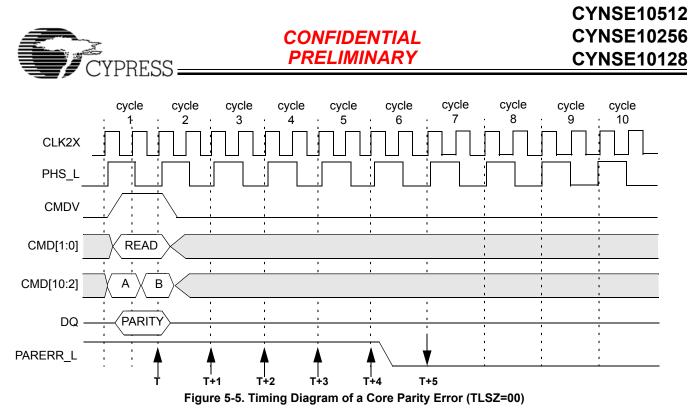

#### Core Parity

The Core includes a one-bit parity for each 72-bit entry in the data and mask arrays. When writing into the data or mask array, the NSE will calculate and generate the one-bit parity for each 72-bit data. Each block also has a block-associated internal register to enable the parity checking for the block (BPAR). When disabled, the block will ignore the Read Parity command.

To issue the Read Parity command, the ASIC issues a Read command and sets the Parity field in the parameters sent through the DQ bus as described in *Table 5-25*. Core parity checking is performed in parallel on four adjacent 72-bit entries per pair of blocks. At the beginning of each parity operation, an internal address counter is incremented. The new incremented address is then used for the parity check operation.

It will cycle through the data and mask arrays as well as odd and even blocks for both arrays for each Read Parity issued. If one or more parity errors are detected, the error is reported in the block's BPAR register. Then all errors are prioritized through an arbiter to select the highest priority parity error, which is then reported in the PARITY register. PARERR\_L will also be set to 0 when there is a parity error. PARERR\_L is valid on the (5+TLSZ)<sup>th</sup> cycle of latency. For example, with TLSZ set to "00" and the command is issued at Cycle1, PARERR\_L will be valid on Cycle6. Read Parity also responds to broadcast CHIPID selection.

*Figure 5-5* shows the timing diagram of a Core Parity error during a Read Parity instruction. The PARERR\_L signal goes Low 5 cycles after the error is detected.

There are two basic flows for parity error recovery. The first flow is by reading the highest priority parity error address stored in the PARITY register, fix the error, decrement the internal address counter and reissue Read Parity. The second flow is by reading the PARITY register to obtain the location, reading the BPAR registers to locate blocks that has the error and then fixing those locations.

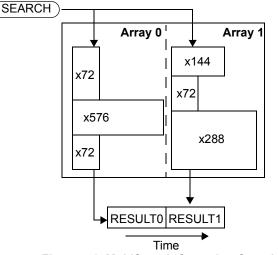

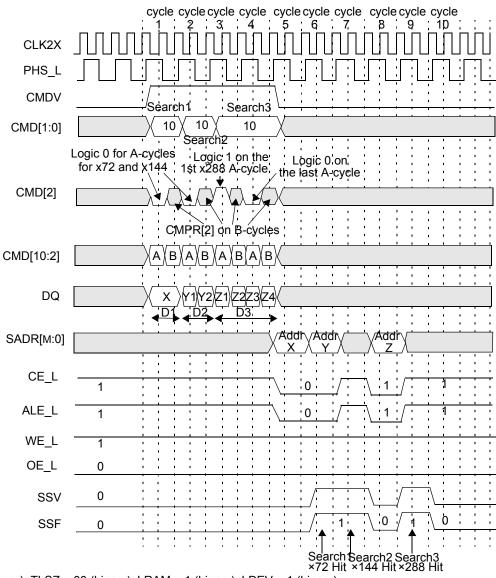

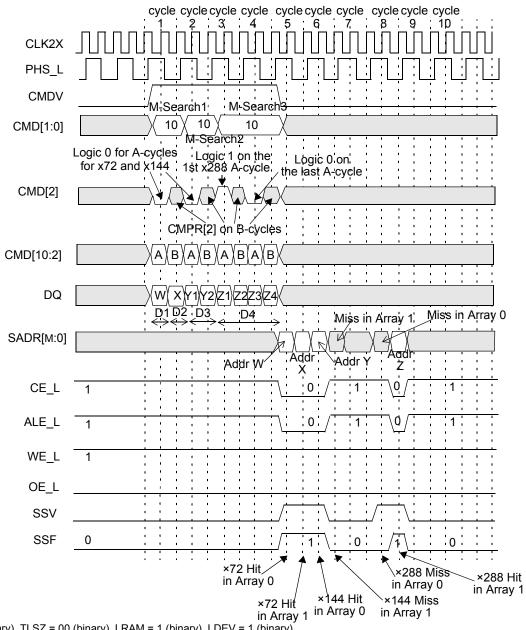

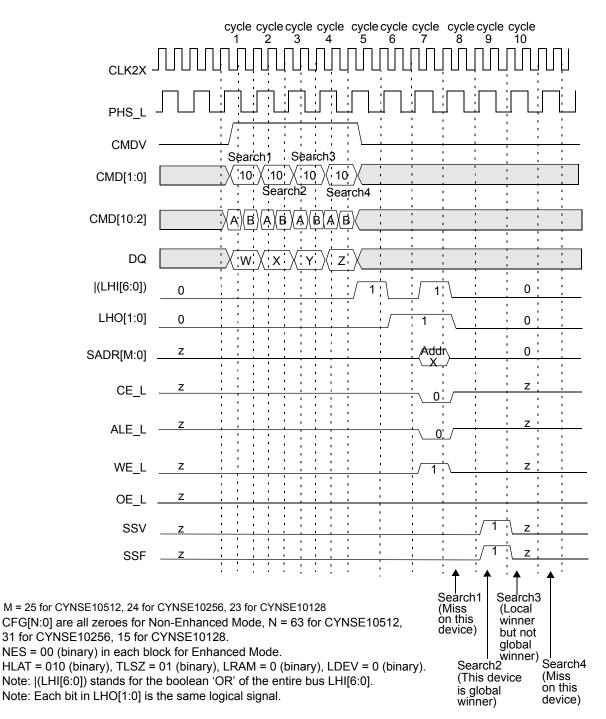

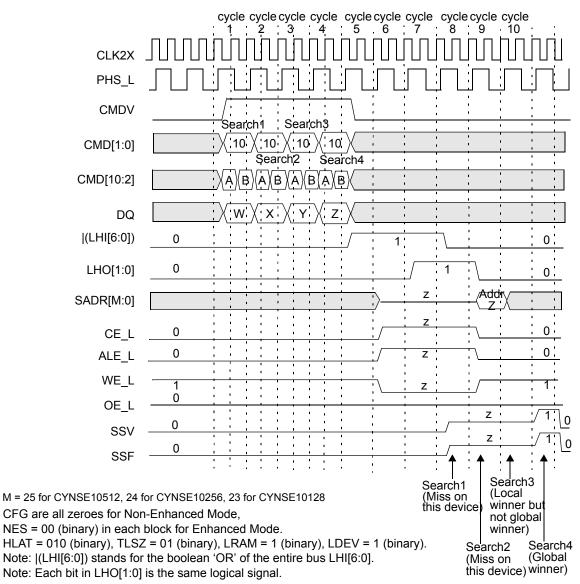

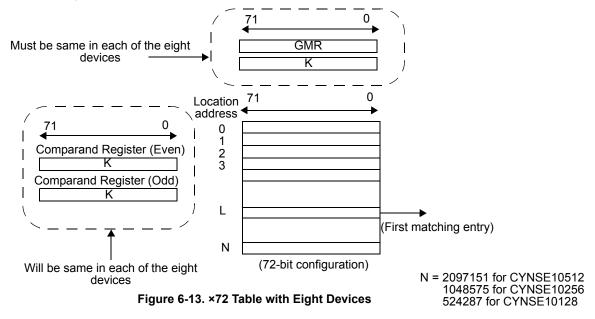

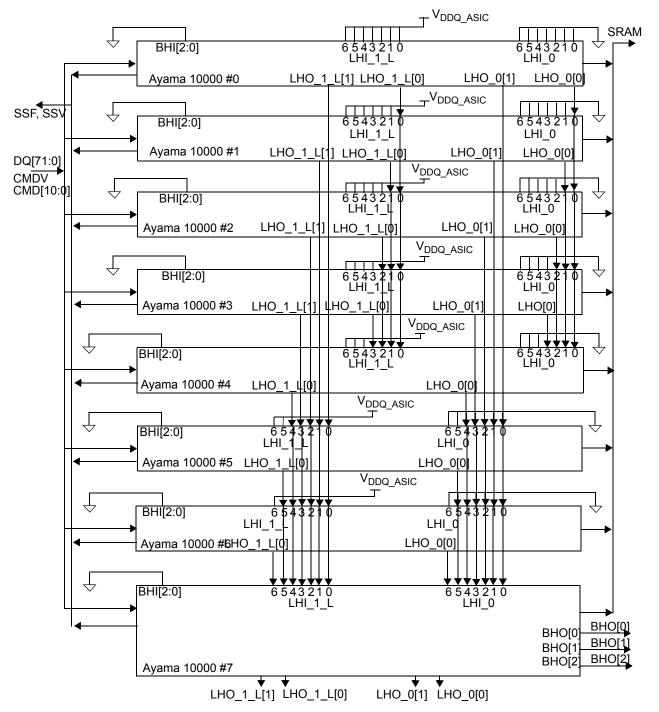

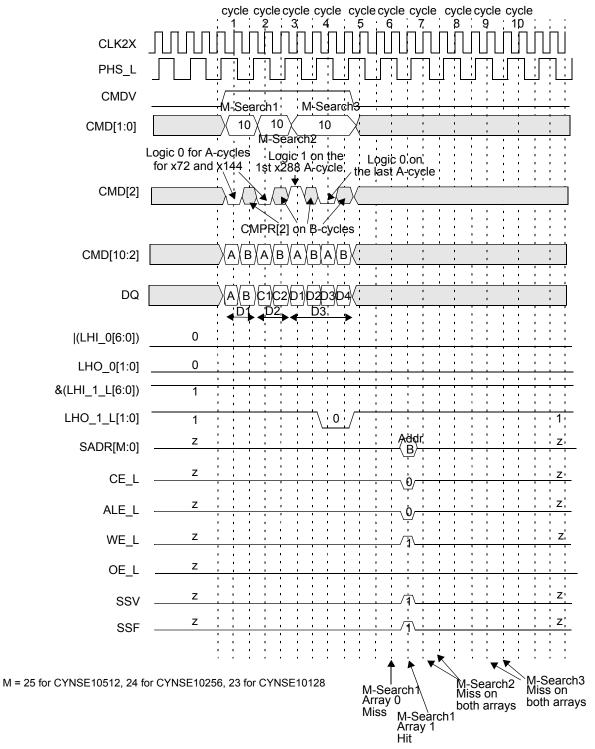

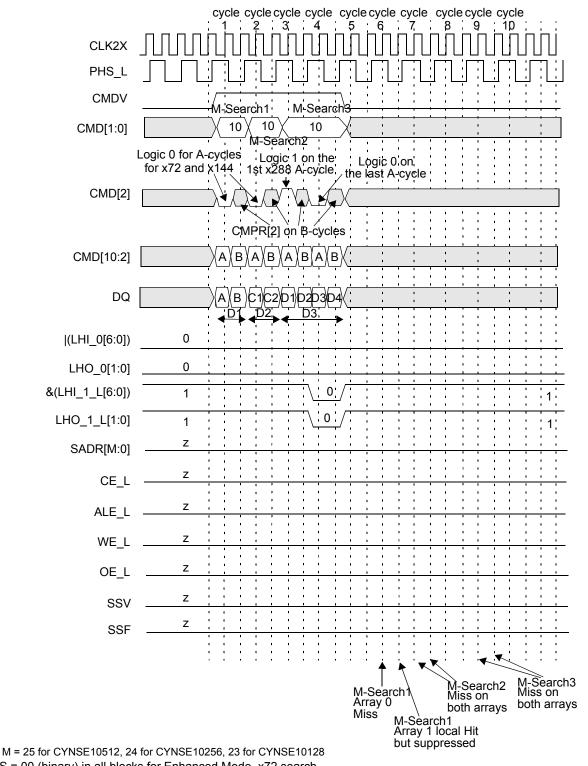

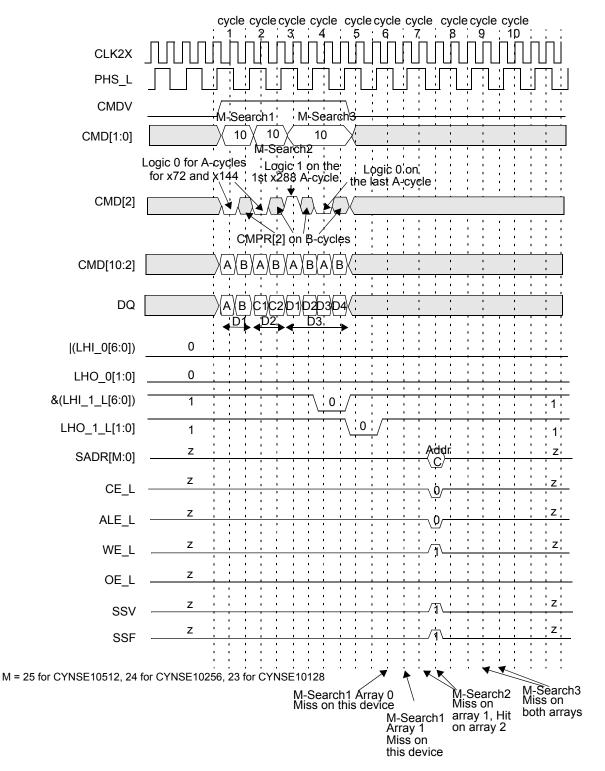

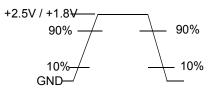

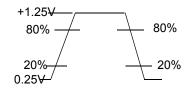

#### 5.1.2.4 MultiSearch